# CHAPTER 1

#### 1.1 Motivation

The recurring demand and aggressive need for the low loss, high linearity, low power, low cost, reduced size and lightweight systems for defence, satellite and wireless applications leads to the search of an alternative technology to solid state devices [1]. These applications need more battery life with improved performance due to their strategic deployment. RF MEMS technology [2-4] is the one which has many current and future applications exacting these qualities include reconfigurable circuits, wireless systems for specific applications, wireless data links, switching networks, RF front end systems, Global positioning systems, phased array systems in radar and EW applications [5-9]. This technology also has the potential to enable wider operational bandwidths and eliminate off-chip passive components by the planar fabrication processes which are compatible with existing IC and MMIC processes for integration [10-12].

Phase Shifters are critical components in the Active/Passive Electronically steerable Antennas (AESA/PESA) for their applications in Missile Seekers, Radar and Electronic warfare systems. AESA/PESA offer many advantages over conventional mechanically scanned arrays such as fast scanning rate, light weight and beam shaping capability. More significantly, AESA/PESA eliminate the requirement of high power concentrated source as each radiating element is fed and controlled individually by the independent transmit-receive modules [13]. The electronic beam steering is best realized by using phase shifters to control the phase of the individual radiating element of the antenna array without any mechanical motion. The beam steering resolution is directly dependent on the number of bits of the phase shifter. Multi-bit phase shifters are used in phased array antennas to minimize the phase

quantization error. In general 3 or 4 bit phase shifters are employed in the commercial systems where as 5 or higher bit phase shifters are implemented in sophisticated military and aerospace applications to meet the high resolution and accuracy requirement [14]. Conventional phase shifters are developed using ferrite types, PIN diodes and MESFET. The ferrite phase shifter can handle high RF power but relatively consume large amount of DC power, expensive to fabricate and require manual tuning. Solid state phase shifters provide a good solution at microwave frequencies and have been used successfully in phased array applications but on contrary these incur high insertion loss leading to high gain requirement at microwave frequencies [15].

Ku band has wide range of applications in Defence and Space domain namely Airborne Radars, Missile Guidance, Collision Avoidance System, Battlefield Surveillance Radar, Missile Tracking and Telemetry as well as in satellite communication [16-18]. Moreover Ku band is a natural choice due its small size antenna and other system requirements. Ku band is also less vulnerable to rain fade than the Ka band frequency spectrum [19]. Practically the insertion loss of the solid state phase shifters in Ku band is of the order of 7-8 dB for 5-6 bit configurations [20]. *There is a need of high resolution, low insertion loss and low power consumption phase shifters in Ku band spectrum.* MEMS based device represent an extremely attractive alternative for the realization of programmable phase shifters.

RF MEMS Phase Shifters have shown their technical promise over the solid state type devices. RF MEMS phase shifters can be designed and developed with different topologies based on the application requirement. The implementation of the MEMS based Phase shifters leads to reduction in power consumption, size and weight which is very crucial for on-board defence and aerospace systems. Replacement by MEMS Phase Shifters even leads to reduction in RF gain requirement in transmit-receive (T/R) modules due to their very low

insertion loss[21-23] which results in elimination of an amplifier stage in the T/R chain. This further leads to reduction in dc power by20-100 mW per element across X to V band frequencies. It is substantial power reduction for space-based, airborne, and even low-power portable telecommunication and radar systems. This aspect becomes more significant as the number of elements in these applications ranges from few hundreds to thousands. MEMS have very low up-state capacitances and result in a wideband performance when compared to similar designs using solid state devices. The switching time of MEMS switches is of the order of 1-50 µs which allows them to be used in virtually all systems except fast airborne applications. The power-handling capabilities of MEMS devices are of the order of mW, which is sufficient for high frequency applications as they are placed before power amplifier in the T/R module. Typically observed millions cycle life time is enough for above mentioned application more specifically for on-board missile systems and single shot defence applications. Hence it is evident that RF MEMS phase shifters can be readily used in the above mentioned applications [24-25].

RF MEMS switch [26-27] is the integral part of the phase shifters and are needed in large numbers (typically 10-20), based on the configuration of the phase shifter. The performance of phase shifter solely depends upon the performance of switch. Electrical performance of solid-state switches degrades drastically beyond a few GHz [28-29]. On the other hand, the MEMS switches provide low insertion loss, high isolation, extremely high linearity and low power consumption over a much wider frequency range [30-31]. In addition non-linearties are non-existent in MEMS device as compared to semiconductor junctions in PIN diodes and GaAs FETs, except for the slight hysteresis noted on the CV characteristics of shunt switches. Their high integration levels and imperceptible inter modulations or harmonics further improve their overall performance. Therefore MEMS based switch are preferred over solid state based switch in reconfigurable and phased array antenna [32]. The

switches can be designed to interface with 50 Ohm impedance across the broad range of frequencies when closed and nearly an open circuit when there is no connection. This property makes them an attractive choice for microwave applications.

The RF MEMS device development has been a challenge and is better understood during recent time. Numerous researchers have reported various analyses for long term operation of these devices. However there have been problems with regard to the stable operation of the RF MEMS devices. In spite of some active research in this area, *stable switching of signals is a problem which stems from the insufficient restoration force*. Also there is lack of sufficient, consistent study in 5-bit phase shifter in Ku band. These necessitate examining some new design with built-in reliability concept and process of these devices as well as development of 5-bit Ku band MEMS Phase Shifter.

## 1.2 Objectives of the thesis

The goal is to design & simulate, fabricate, characterize and optimize the RF MEMS switch and phase shifter for reconfigurable circuit and phased array applications respectively. Keeping the gaps in literature review, the following specific objectives are formulated for this thesis.

- I. Design, simulation and Analysis of RF MEMS device i.e. switches for its performance and highlighting the challenges with built in reliability having low actuation potential.

- II. Prototype fabrication, inspection and characterization of the capacitive and ohmic switches for a successful implementation in the Phase shifter circuits.

- III. To Design, fabricate & demonstrate the development of the 5-bit RF MEMS based Phase Shifter in Ku band for implementation in Transmit-Receive Modules of Active Phased array application.

#### 1.3 Thesis Outline

The thesis has been framed in nine chapters. First chapter discusses the motivation and objectives. The second chapter briefs the literature survey of the existing work. The third chapter summarizes the Design & Simulation of the shunt and ohmic RF MEMS switches. The fourth chapter contains the prototype fabrication, experimental set up, results & discussion of the RF MEMS switches on quartz. The fifth Chapter illustrates the Design & Simulation of the MEMS Phase Shifter configurations for Ku band. The sixth chapter deals with the Fabrication & Process Inspection of the phase shifter. The seventh chapter presents the On-Wafer RF Characterization of Single bits and 5 bit Phase Shifter. The eight chapter explains the control circuit and test jig development and the presents the results of microstrip Phase Shifter Characterization. Finally in chapter nine conclusion and plan for future work are outlined.

# **CHAPTER 2**

#### LITERATURE SURVEY

As described in the objective of the thesis, the aim of this work is to develop a 5 bit RF MEMS phase shifter in Ku band due to its application requirement in the Defence and Aerospace domain. The switch being an integral part of the phase shifter, the literature survey was focused on these two devices i.e. phase shifter and switch. This section describes the work carried out by the various researchers and their results. The gaps observed in the results are also discussed.

# 2.1 RF MEMS Switch – Brief Description and Fabrication

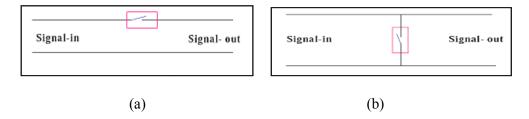

There are two basic design topologies namely shunt and series [33] switch used in RF to mm wave frequency. The ideal series switch results in an open circuit in the transmission line when no bias is applied called the up state. It results in a short circuit in the t-line when a bias voltage is applied. Ideal series switches have infinite isolation in the upstate and zero insertion loss in the down state position. The shunt switch is placed between transmission line and the ground depending upon the bias voltage; it either leaves the t-line unaffected or deflects it to ground. Therefore, the shunt switch [34] results in very low insertion loss when no bias is applied for up-state position and high isolation when bias is applied for down-state position. Shunt capacitive switches are more suited for higher frequencies in the GHz range. It is to be noted that both metal-metal and capacitive contact can be used in series and shunt configurations. However, it is preferred to use metal-metal contact switch in series

configuration and capacitive contact switch in shunt configuration. Simple illustrations are given below in Fig. 2.1 (a) for the series and (b) the shunt switch configurations.

Fig. 2.1: (a) Series Switch - Output is "High" when switch is closed and (b) Shunt Switch - Output is "Low" when switch is closed.

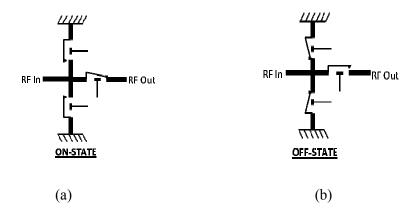

The combined functioning of the switches is also illustrated by the sketches drawn in Fig. 2.2 (a) and (b) to achieve high isolation. Figure 2.2 (a) shows the on state whereas in the Fig. 2.2 (b) it is off as the states of the switches are just in opposite condition. The RF signal in the Fig. 2.2 (b) is grounded and high isolation can be achieved.

Fig. 2.2: (a) and (b) Signal transmission flow of combined switches to achieve the high isolation.

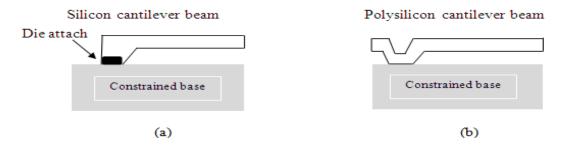

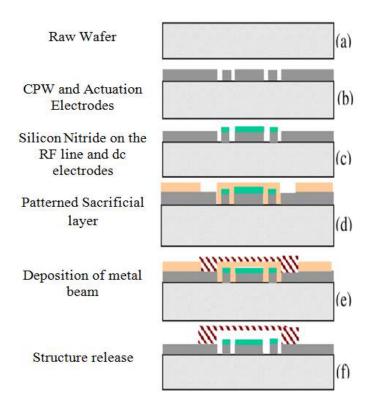

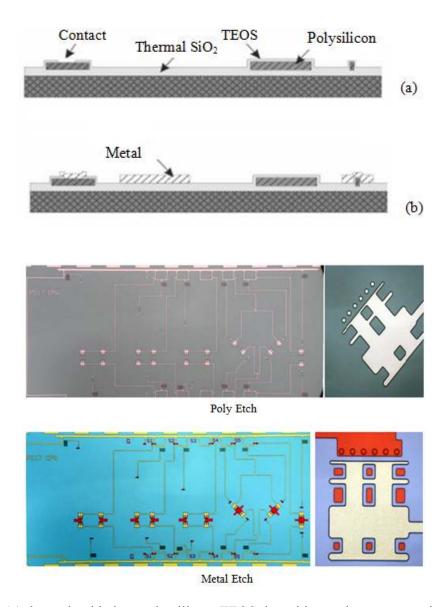

Micromachining techniques have been evolved for MEMS fabrication [35]. These include the bulk and surface micromachining. In contrast to the bulk micromachining in which substrate material is removed by means of the physical or chemical means, the Surface micromachining builds microstructure by adding materials layer by layer on top of the substrate. In this process of adding and removing layers different structures are realized and interconnected using the multi mask fabrication process.

The use of bulk micromachining in fabrication of RF MEMS switches is very limited. Moreover it is very difficult to integrate the MEMS devices fabricated using this technique with IC components required for signal conditioning. Thus RF MEMS switches are almost exclusively fabricated using the surface micromachining technique [36]. The surface micromachining technique is best suited to integrate mechanical devices with integrated circuit (IC) components because this technique utilizes deposited thin films for fabrication of mechanical parts of the sensor. Figure 2.3 (a) and (b) shows the typical difference between the two techniques used for producing a micro cantilever beam [37-38].

Fig. 2.3: (a) Bulk micromachining (b) Surface micro machining.

As the processes for fabrication of the mechanical parts are similar to those for IC components with some additional steps, integration of MEMS and signal conditioning circuitry may be possible. As discussed in the previous section, fabrication of cantilevers or fixed-fixed beams is essential for realization of RF MEMS switches. The process can be modified for different materials for the beam, post and substrate. Also, some applications require complicated surface micromachining processes where many layers have to be deposited and selectively etched to realize the final structure. RF MEMS switch is one such application where typically five to eight masks may be needed to realize the full device. This is a multi-mask process device fabrication and selection of the sacrificial layer is very crucial. Many Researchers have used many materials as the sacrificial layer, out of these, photo resists [39-40] and polyimide [41] is very popular because these can be removed easily by

oxygen plasma [42] without affecting the membrane material. Hence selection of sacrificial layer has to be done keeping in view the process of removal.

### 2.1.1 RF MEMS Switch - Technology Development

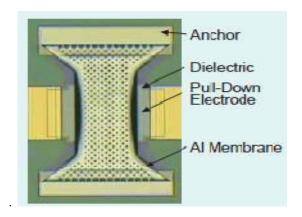

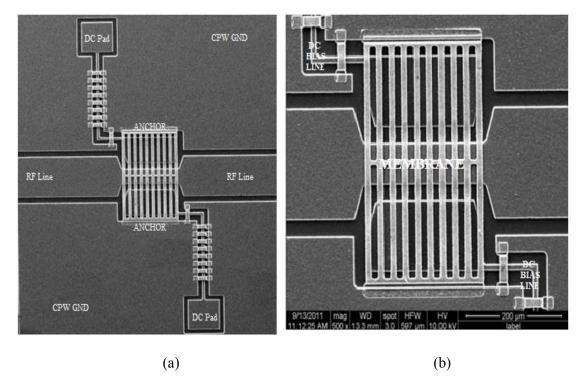

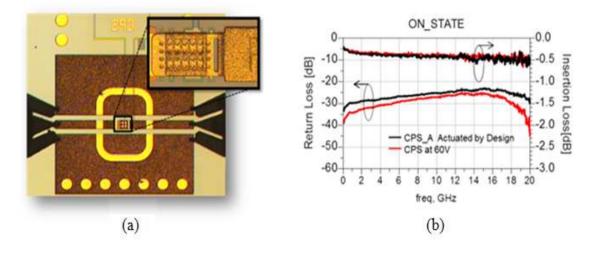

Texas Instruments (now Raytheon) developed the first practical MEMS capacitive shunt switch Fig. 2.4 [43-44]. The switch is based on a fixed-fixed metal (Al or Au) beam design. The anchors are connected to the coplanar-waveguide ground plane, and the membrane is, therefore, grounded. In a microstrip implementation, the switch anchors are either connected to the ground plane using via holes or using a  $\lambda/4$  radial stub. In the Raytheon design, a center pull-down electrode is used and a 1000-2000-Å silicon-nitride layer is used to isolate the metal membrane from the pull-down electrode. The actuation voltage was observed between 3-50V. The above mentioned studies do not cover the electromechanical analysis.

Fig. 2.4: Raytheon capacitive shunt switch [44].

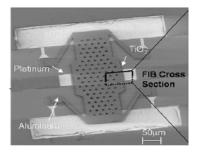

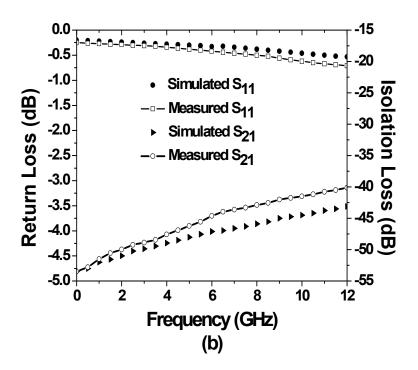

Fernandez –Bolanos et al. proposed RF MEMS capacitive switch with low actuation voltage with excellent capacitive ratio close to 200 using TiO<sub>2</sub> as dielectric as shown in Fig. 2.5. This design uses low loss high resistivity silicon substrate [45]. It has an insertion loss less than 0.5dB and isolation more than 20dB at 20GHz at a low actuating voltage of 8V. This reported work on switch lacks the study on parameters such as spring constant and

restoring force. Keeping in view the low actuation voltage these parameters become critical for long term operation.

Fig. 2.5: SEM View of the MEMS switch [45].

S. Pacheco et al. of the University of Michigan presented a low spring-constant membrane capacitive switch [46]. The membrane is connected using a folded spring to the anchors and the spring constant can be lowered to 1-3N/m with the use of several turns as shown in Fig. 2.6. This result in a pull-down voltage of 8-15 V and a relatively low switching speed of 30-40µs. Since the restoring forces are low for such a design, these switches are useful when integrated with a pull-up electrode placed 1-2µm above the movable membrane. Another X and K band SPDT switch was also developed using the same configuration [47]. It has been mentioned in the study that the problems with low spring constant is their sensitivity to mechanical forces such as acceleration, vibration and the associated slow response times.

Fig. 2.6: Low spring-constant MEMS switch [46].

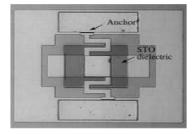

The LG KOREA developed a very-high-capacitance-ratio MEMS shunt switch [48-49] as shown in the Fig. 2.7. The design is based on the standard fixed–fixed beam capacitive shunt switch and uses strontium-titanate-oxide (SrTiO3) as the dielectric layer. STO results in

a relative dielectric constant of 30–120 with a low loss tangent (0.02) and very low leakage current. The fabricated switches achieved a capacitance ratio of 600 and a down-state capacitance of 50 pF (up-state capacitance of 70–80 fF). The pull-down voltage of 8 V has been reported due to the low-spring constant support structure. The switch isolation is better than -40dB at 3-5 GHz. The reported work does not explain the effects of low pull-in voltage for the stable operation of the switch.

Fig. 2.7: LG-Korea high-capacitive-ratio MEMS shunt switch [49].

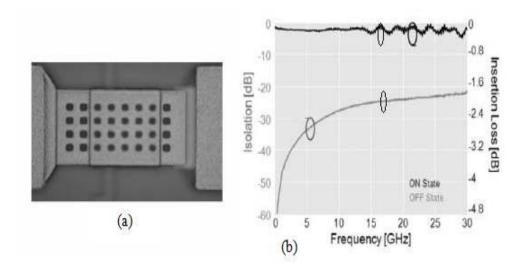

S C Shen et al. of University of Illinois developed a low-voltage DC-contact shunt switch [50-51]. The low-voltage design is achieved using narrow low-spring constant support beams near the membrane anchor. The switch consists of two pull-down electrodes on both sides of the center portion of the switch as shown in the Figure 2.8. The actuation electrode area is (2) x 800 x 100 mm<sup>2</sup> and the resulting pull down-voltage is 9–16 V.

Fig. 2.8: SEM view of DC-contact MEMS shunt switch of University of Illinois [51].

Richard Chan et al. of University of Illinois investigate the performance and lifetime of a metal-to-metal shunt RF MEMS switch fabricated on an SI–GaAs substrate [52-53]. The reported switch is a shunt bridge design that is compatible with standard microelectronic processing techniques. The RF performance of the switch includes isolation better than 20 dB

from 0.25 to 40 GHz and switching speeds of less than  $22\mu s$  with actuation voltages less than 15V. The switch structure includes separation posts that eliminate sticking failure and has demonstrated lifetimes as high as  $7x10^9$  cold switching cycles. These results show that good reliability is possible with a metal-to-metal RF MEMS switch operated with a low actuation voltage.

V Milanovic et al. of University of California, Berkeley developed a process for the transfer of MEMS switches from a low-resistivity silicon substrate to a quartz substrate [54-55] as shown in the Fig. 2.9. This allows the MEMS switches to be fabricated using standard CMOS techniques and then transferred to a microwave-compatible substrate. They have developed three switches using this technique: a DC-contact series switch using a fixed–fixed beam design and a DC-contact shunt switch. The actuation voltage varies from 30 V to 110 V and it is due to chip-to-chip variation in the height of the transferred MEMS structures.

Fig. 2.9: Berkeley see-saw series/shunt MEMS switch [54].

S Pranonsatit et al. of Imperial College London, U.K [56] demonstrated single-pole eight-throw radio-frequency (RF) MEMS rotary switch, the concept of this rotary switch is based on the adaptation of the axial gap wobble motor [57]. A prototype switch has been made using separately fabricated stator, rotor, and cap components that are then assembled. An average contact resistance of 2.5 was recorded. However, values as low as 1.0 was also found. The assembled rotary switch demonstrated an excellent RF performance. With the inclusion of feed lines, the insertion loss was 2.65dB at 20 GHz after renormalizing the measurement

reference impedance. When the loss of the feed lines is subtracted, the worst-case ON-state intrinsic insertion loss of the rotary switch is only 2.16 dB at 20 GHz.

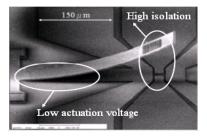

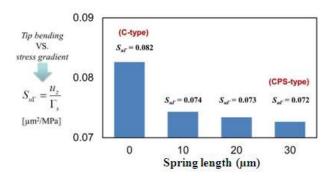

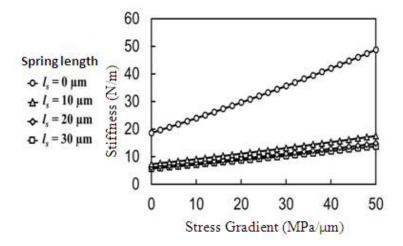

Chia-Hua et al. of National Taiwan University achieved low pull-in voltage and high isolation of the switch by exploiting buckling and bending effects induced by well-controlled residual stress [58]. The minimum actuation voltage of the fabricated switch was measured to be 10.2 V. They achieved insertion loss and isolation of 0.21 dB and - 44 dB respectively at 5 GHz. Figure 2.10 shows the SEM image of their switch.

Fig. 2.10: Switch from National Taiwan University using controlled residual stress.

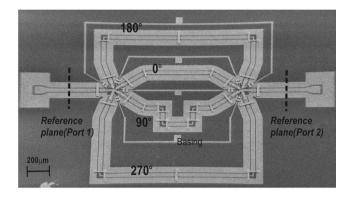

M. Tang of Nanyang Technological University, Singapore fabricated a shunt switch by forming a basin in silicon which partially defines the gap between membrane and down electrode for X-band application [59]. In this configuration, the ground line was restricted from the basin. Figure 2.11 (a) and (b) shows SEM views of their switch where single and double bridge was fabricated to achieve the high isolation at resonant frequency. They achieved the isolation loss of 16.5-28dB and 25-35 dB for the single and double bridge respectively in the frequency range 10-13GHz and a pull-in voltage of 20.4V.

Fig. 2.11: Nanyang Technological University shunt switch in (a) single bridge (b) double bridge configuration.

Wei-Bin Zheng of Southeast University Nanjing, China fabricated shunt RF MEMS switch for X-band application on GaAs substrate [60]. They achieved an isolation of -42dB at self resonant frequency of 24.5 GHz. The insertion loss between 1 to 25.6 GHz was less than 0.25dB and actuation voltage was 17V. They demonstrated life time as long as  $5 \times 10^5$  cycles.

Puyal et al. of Centre National de la Recherche Scientifique (LAAS-CNRS) France, [61] presented the scalable shunt switches models with different sizes ranging from 350x340 μm² to 800x1000 μm² for varying resonant frequencies. The insertion loss in the range 1.1 dB to 0.3dB was reported up to W band with actuation voltage ranging from 20 to 35V. The SEM photos are shown in the Figure 2.12 with holes on the beam. *The study does not explain the effect spring constant effect arising due to the change in mass because of dimensions and holes variation in the beam.*

Fig. 2.12: SEM images of differnt configurations [61].

H. U. Rahman et al. of University of New South Wales, Australia [62] presented a simple low actuation voltage series switch at 6.39V as shown in the Figure 2.13. The low actuation voltage has been achieved by varying the cantilever dimensions. *This work does not cover the effect of very low actuation voltage on the restoration force which has a direct bearing on the stable operation*.

Fig. 2.13: SEM image shows the cantilever of the switch.

They also fabricated the non standard cantilever beam designs [63]. A mechanical modelling was presented based on the Euler–Bernoulli beam equations. The SEM photo is shown in the Figure 2.14. The fabricated switches using these cantilever beams exhibited 23V actuation voltages using a dry-release technique. The isolation was better than 27dB, from 0 to 40GHz. The insertion loss of 1.3dB was achieved and results were not in consonance to simulated performance in terms of insertion loss. This is high insertion loss which does not exploit the MEMS technology advantage. The emphasis on the spring constant was concentrated and does not include the stress analysis on the cantilever.

Fig. 2.14: SEM image shows the top view of the switch [63].

Based on above exhaustive literature survey we found that there is need to address some of technology issues more thoroughly, such as high restoration force for low pull in voltage, stress effect, easy removal of sacrificial layers and in-built reliability of MEMS switch through design. Brief details and associated challenges are discussed in following section-

**Pull-in voltage** in the electrostatic actuation of the RF MEMS devices is a significant parameter. A low pull-in potential has many advantages. Mainly it allows the switches to be easily integrated with additional circuitry as it reduces the burden of resorting to voltage boosting circuits and saves precious substrate area. Secondly, it reduces the power dissipation which is proportional to the square of the voltage between the signal line and membrane in the down-state. Most significantly, a low pull-in voltage improves the reliability as there is

less charge injection into the insulting layer due to reduction in electric field across it [64] in the down-state of the switch. This charge in the insulating layer alters the pull-in voltage and in the extreme case may result in the switch being permanently in either the upper or lower state by keeping switch permanently on or off. This is a serious reliability problem of capacitive switches. C. L. Goldsmith et al. reported that the lifetime of capacitive switches strongly depends on the actuation voltage [65]. Reduction in pull-in voltage also allows lesser insulator thickness resulting in higher capacitance in the "OFF" state ( $C_{\rm off}$ ). This improves the  $C_{\rm off}/C_{\rm on}$  ratio of the switch, thus improving the device performance. Thus in this work, low pull-in voltage structures with sufficient restoration force for capacitive shunt-type and ohmic series switches have been considered for study.

It is known that a low pull-in voltage [66] can be achieved by reducing the gap between the signal line and membrane, or by increasing the effective overlapping area between membrane and bottom electrode or by designing a membrane of low spring constant [67]. While reducing gap or increasing overlap will increase insertion loss due to increase in C<sub>on</sub>, reducing the spring constant (K) of the membrane presents more flexibility [68] in achieving low pull-in voltage without affecting the switch performance at higher frequencies. The design of membranes of low spring constant to reduce pull-in voltage at the cost of restoration force is a serious concern. Moreover, release of a membrane of low spring constant is difficult due to stiction forces. We undertake this challenge in our work by novel design of switch structure.

Any Stress in the released membrane is major issue for all MEMS application. The type and the quantity of the stress changes from design to design, process to process and the also depend on material of the membrane. The beam or cantilever design is the key factor for stresses which can result after the fabrication. The mechanical design and analysis are to be uniquely carried to have built-in reliability. A compressive stress in a membrane may permanently close the switch whereas a tensile stress may increase the pull-in voltage of a

membrane. As we have already discussed that a high pull-in voltage of membrane can lead to a charge injection in dielectric material and hence affect the reliability of the switch in long run. So the material properties of the membrane should be characterized thoroughly in same ambient condition before it has to be used in actual device fabrication. So overcome this challenge selection of the test structures and characterization techniques should also be done appropriately to achieve accurate results. *In this work, the actual design of the membrane is used to minimize the effect of stress on the membrane.*

#### 2.2 RF MEMS Phase Shifter

A phase shifter [69] is a two-port network with the provision that the phase difference between output and input signals can be controlled by a control signal, usually dc bias. Phase shifters with low insertion loss, low drive power, continuous programmability and low production cost are the key to the development of lightweight Active phased array systems. Currently Phase shifters are based on ferrite materials, pin diode and FET switches. Each type has its own advantage in terms of power handling and switching speed etc. The p-i-n based devices consume more dc power while solid state type incurs high insertion loss. Solid-state phase shifters provide a good planar solution at microwave frequencies and have been extensively used in modern phased-array systems. Whereas MEMS type phase shifters are finding its place due to its technical superiority in terms of very low insertion loss, virtual no power consumption, high linearity and bandwidth. In general the micro-electromechanical phase shifters under development are based on the MEMS based switches which have replaced the solid state switches. MEMS switches incur low loss and these have very low up state capacitance which results in a wide band performance when compared to similar designs using solid state devices.

# 2.2.1 RF MEMS Phase Shifter Configurations

Most of RF MEMS phase shifters developed are based on the established designs except that the solid-state switch is replaced by a MEMS switch. The preferred approaches are discussed in this section.

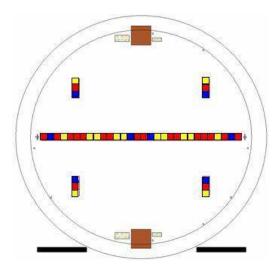

In case of the **distributed type** t-line is periodically loaded with the variable capacitors. The change in capacitance influences the phase velocity of traveling electromagnetic wave causing a phase delay and thus acts as delay line. The distributed approach consists of a high impedance line (> 50 ohm) which can be easily implemented using coplanar waveguide as shown in Fig. 2.15 [70-71]. The periodic spacing and the number of bridges depend upon the design. The key technology developments for realization of DMTL delay line are actuation mechanism and the precise control of processes, as transmission line properties are sensitive to geometric tolerances. For given substrate and frequency band phase shift can be varied by difference of loaded line impedance [72]. In general DMTL approach is preferred for 30GHz and above.

Fig. 2.15: Distributed transmission line digital phase shifter [72].

The **reflect line** phase shifter can be implemented using a succession of MEMS series or shunt switches on a transmission line. The reflect-line design results in double the phase delay per unit length as compared to the standard design [73]. The electrical separation between the switches is thus equal to the half of the lowest resolution bit. Figure 2.16 shows the general approach of the reflect line phase shifter configuration. The coupler needs larger area for realization along with MEMS switches.

Fig. 2.16: Configuration of the reflect line phase shifter [73].

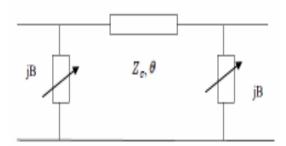

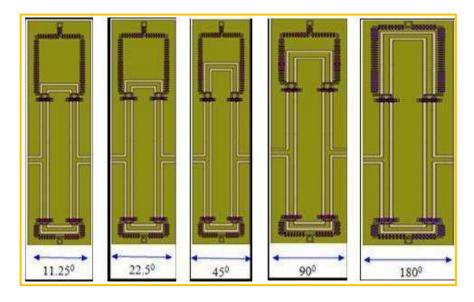

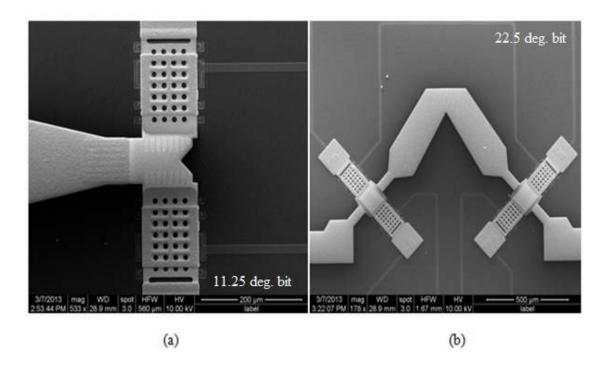

**Loaded line** phase shifters are designed by loading t-line with two different impedances and use a midsection matching network [74-75]. Figure 2.17 shows the sketch of the loaded line design topology. The matching network ensures that phase shifter is matched to  $Z_0$  for both loading conditions. Loaded line phase shifters yield excellent performance for small phase delays like 11.25° and 22.5°. The higher bit design does not provide accurate results in terms of phase control. The loaded line phase shifters can be cascaded in series to result in any required phase shift due to their perfect match. RF MEMS switches can be used to load the line.

Fig. 2.17: Loaded line phase shifter configuration [74].

**Switched line** is one of the most adopted topology as it can achieve the digital phase shifter by using switched delay line technique. In this approach each delay bit is implemented separately and an N bit phase shifter is designed using a succession of several bits of different values [76-77]. The phase delay is obtained by switching in the required number of bits. Switched line phase shifters can be fabricated using series or shunt switches. A sketch of the

four bit is shown as below in the Figure 2.18. A 'T' junction at the input and the output is connected through the transmission line via MEMS switches.

Fig. 2.18: Switched line phase shifter configuration [76].

The lower part is shown as the reference path with two switches in each bit. The upper path or the delay path is connected through the switches in the similar way. The signal passes through the reference path when these switches are in 'ON' state and upper path switches are in the 'OFF' state and vice versa.

### 2.2.2 RF MEMS Phase Shifters- Technology development

RF MEMS Phase Shifters find application in airborne and space-borne radar sensors which do not require long range search and track capability. The low-altitude unmanned aerial vehicles offer potential for RF MEMS Phase Shifters. Unlike RF MEMS resonators, RF MEMS Phase Shifters have not been commercialized. The initial MEMS Phase Shifters research companies include Raytheon, DARPA, MEMTronics, Radant MEMS, Wispry and XCOM wireless. The most required applications are in the frequency bands namely X, Ku, Ka, V and W for the RF MEMS Phase Shifter development. The switching time of MEMS type phase shifters is of the order of 1-50 µs which allows them to be used virtually used in all systems except fast switching speed required systems. The following is the literature details of earlier work done on the RF MEMS Phase Shifters.

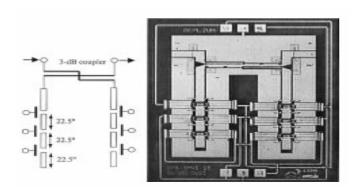

Raytheon developed 2 bit and 4 bit X band MEMS Phase shifters using reflect line topology on  $500\mu m$  Si/Al<sub>2</sub>O<sub>3</sub> thick substrate [78]. The reported average insertion loss was 0.65 dB and 1.15 dB respectively with phase error of the order  $\pm$  11 degree. The die area for the 2 bit is  $50 \text{ mm}^2$  and  $100 \text{ mm}^2$  for 4 bit.

B. Pillans et al. reported ka band phase shifter (32-36 GHz) using switched line topology [79]. He reported average insertion loss of 2.25 dB with phase error 13 degrees. The image is shown in the Figure 2.19. *Above works have high phase error and the large substrate area*.

Fig. 2.19: Raytheon phase shifter [79].

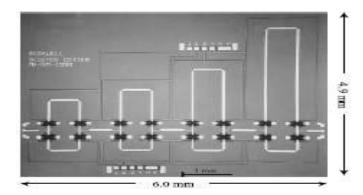

Rockwell reported a pioneer work using series (SP4T) switched line topology on 200µm GaAs substrate [80-81]. The average insertion loss was 0.6 dB and 1.1 dB for the 2 bit and 4 bit types.

J.F DeNatale developed 35-50 GHz 3 bit phase shifter with 2.2 dB insertion loss fabricated on 75μm GaAs substrate using switched line topology [82]. *The 75μm substrate lack integration to other devices and lead to higher insertion loss*.

Rockwell Science Center developed a 4-bit DC-40-GHz True Time delay network phase shifter using metal to metal contact RF MEMS switches [83-84]. The phase shifter is built on a 75-µm-thick GaAs substrate. The average insertion loss is -2.2dB at X-band. The study suggested that loss improvement to -1.4 dB for the 4-bit design if the phase shifter is

integrated on a 200-µm GaAs substrate. The area of the 4-bit X-band phase shifter is 30 mm<sup>2</sup>. Figure 2.20 displays the image of the die.

Fig.2.20: Rockwell DC-40 GHz switched line phase shifter [83].

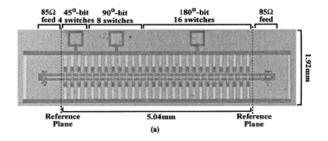

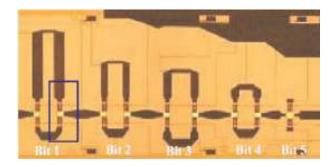

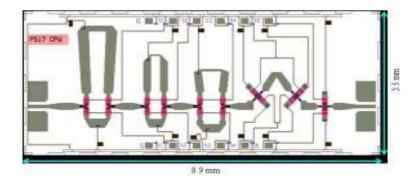

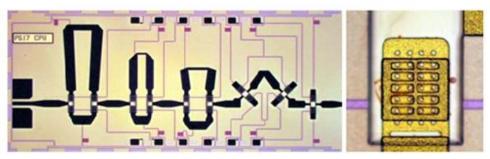

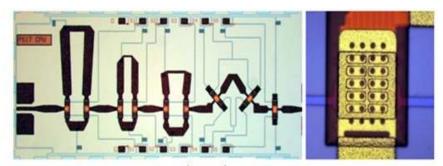

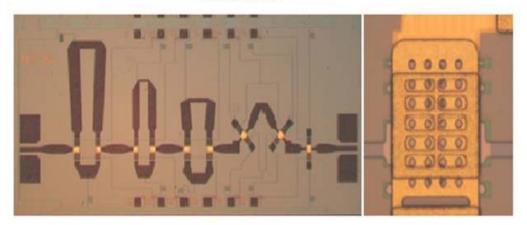

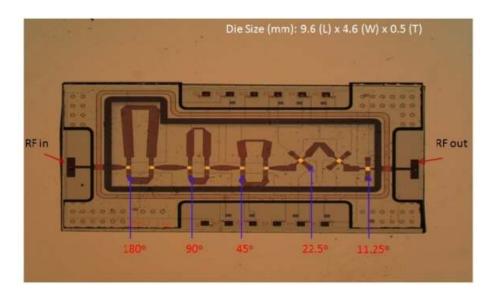

Nanjing Electronic Devices Institute China presented a development work in X-band by fabrication of the compact 5-bit Switched Line Digital MEMS Phase Shifter on HRS with overall chip size of 7mm x 4 mm [85]. He reported using 3 port MEMS switch resulting into a compact design. The Phase shift error is within 5° and insertion loss is 3.6 dB at 10 GHz. There is a scope of improvement in terms of the insertion loss with phase error with in 3° in this frequency range. The photo is shown in the Figure 2.21.

Fig. 2.21: Nanjing Institute phase shifter [85].

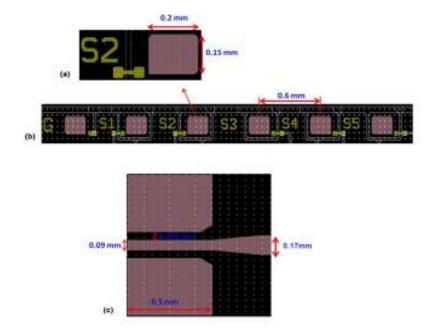

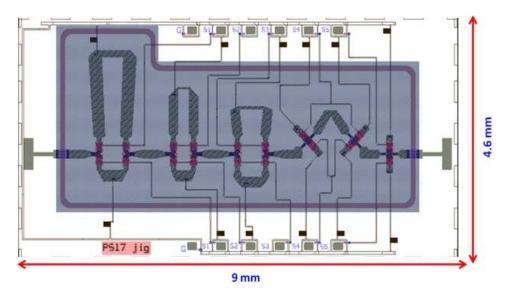

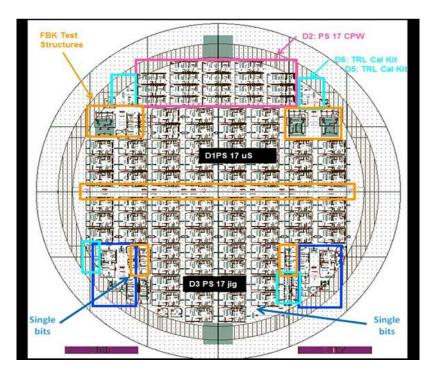

University of Perugia Italy presented a pioneer work of design and manufacturing of a 5 bit K-band MEMS phase shifter by employing different switch configurations namely cantilevers and air bridges in the form of SP2T and SP4T at RF junctions [86-87]. These were fabricated monolithically using 200µm thick HRS at FBK foundry. The three

configurations were optimized and SP2T based option found to be best trade off. It is reported that this option has the insertion loss of 2.2 dB with insertion loss variation within  $\pm 0.4$  dB with foot print area as  $6.5 \times 3.2 \text{mm}^2$ . They also presented the packaging of the phase shifter die and reported an addition of insertion loss of 1.8dB at 20.7 GHz. *The packaging loss is higher in comparison to the phase shifter insertion loss and there is scope of packaging optimization for electrical performance*. The image of the die is shown in the Fig. 2.22.

Fig. 2.22: Image of the University of Perugia phase shifter [87].

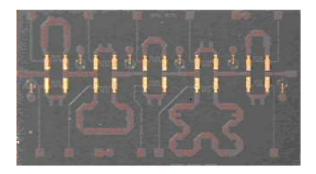

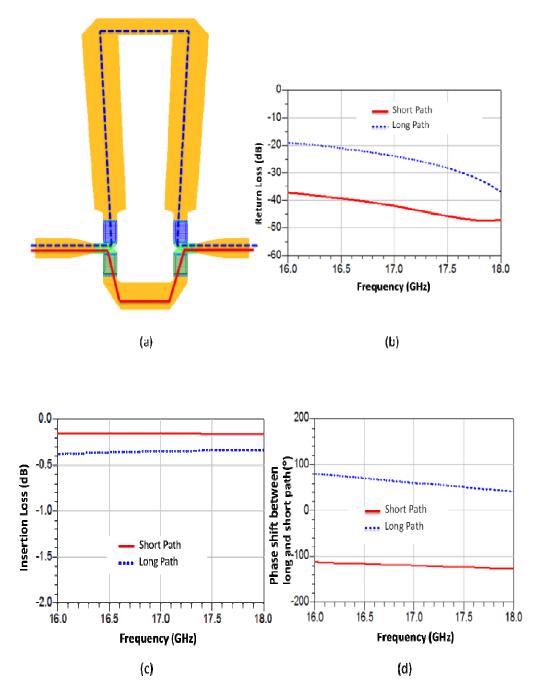

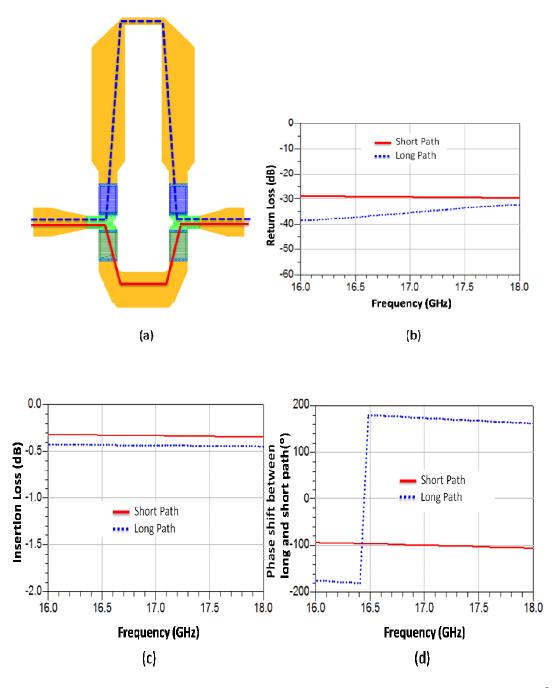

GAO Yang et al. fabricated a 4-bit MEMS switched-line phase shifter which is composed by MEMS SP4T switches and micro-strip transmission lines and works in X-band [88]. Each MEMS SP4T switch is used to switch two different signal pathways, reference phase signal pathway and delayed phase signal pathway. Each MEMS SP4T switch consists of 4 contact type RF MEMS switches with cantilever beam movable contact structure. The simulation results show that the return loss and insertion loss of SP4T switch are -36 dB and -0.18 dB at 10 GHz respectively. Figure 2.23 shows the image of the phase shifter.

Fig. 2.23: Hybrid integrated 4-bit MEMS switched-line phase shifter [88].

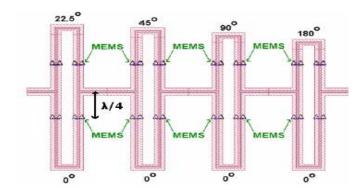

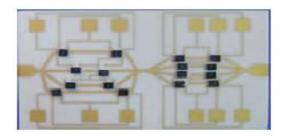

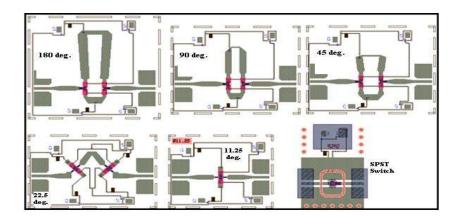

Young J Ko et al. designed an integrated 3-bit RF MEMS phase shifters comprising of the three different 1-bit phase shifters with 11.25°/22.5°/45° stub-loaded line phase shifters [89]. The fabricated 3-bit phase shifter has insertion loss of avg. -2.0 dB and return loss of min. -10dB with phase error of average 2.0° at the frequency ranged between 10.7-12.75 GHz. The die size of 25 mm<sup>2</sup> has been reported.

Robert Malmquist et al. designed a 4 bit digital type MEMS phase shifter and optimized for 35 GHz [90]. This design has been implemented on a 525 µm thick quartz substrate. The two smallest bits are implemented using loaded-line techniques whereas the two largest bits are made using switched delay lines. The circuit area is 5x 11 mm<sup>2</sup>.

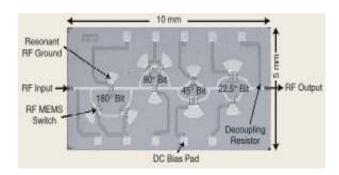

Nickolas Kingsley et al. presented a 4-bit MEMS phase shifter fabricated, integrated, and packaged into an organic flexible low-permittivity material [91]. A microstrip switched-line phase shifter has been optimized at 14 GHz for small size and excellent performance. In addition, the MEMS phase shifter was packaged in an all-organic flexible low permittivity liquid-crystal polymer (LCP) package. For the 4-bit phase shifter the worst case return loss is greater than 19.7 dB and the average insertion loss is less than 0.96 dB. The reported average phase error is 3.96°.

Songbin Gong et al. developed a 2-bit switched-line phase shifter using dc-contact single-pole four-throw (SP4T) RF micro-electromechanical switches at 60-GHz [92]. The phase shifter demonstrates an average insertion loss of 2.5 dB in the 55–65 GHz band with a return loss better than 12 dB for each state. The phase error for each state of the switched-line phase shifter is less than 1° at 60 GHz. Figure 2.24. Shows the image of the 2 bit phase shifter developed.

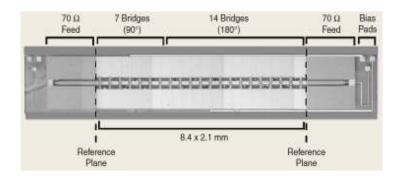

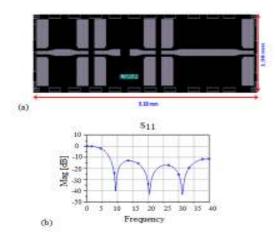

JS Hayden et al. of University of Michigan fabricated a 2-bit Ka-band distributed phase shifter on a quartz substrate using coplanar waveguide (CPW) lines and RF MEMS capacitive switches [93-94]. The developed phase shifter is shown in the Fig. 2.25. The

phase shifter consisted of 21 sections with a spacing of 400  $\mu$ m resulting in a total length of 8.4mm.

Fig. 2.24: SEM images of the fabricated V -band 2-bit phase shifter [92].

The performance of distributed phase shifters is strongly dependent on Q of the loading capacitor. This was achieved using metal-air-metal capacitors at Ka-band frequencies. The 2-b phase shifter results in an average insertion loss of -1.5 dB.

Fig. 2.25: University of Michigan DMTL phase shifter [94].

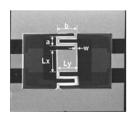

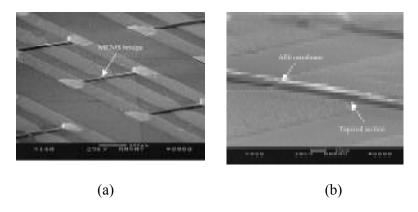

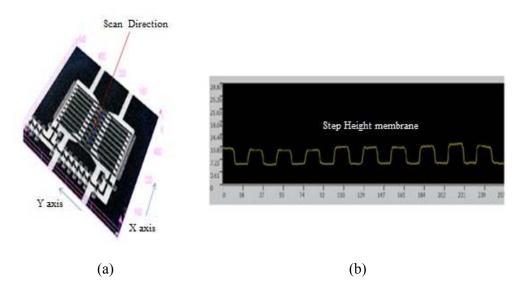

Jian Qing et al. describes the design, fabrication, and testing of distributed MEMS phase shifters for Ka-band communication systems [95]. The phase shifters are fabricated on the high-resistivity silicon substrate using suspended AlSi bridge membrane. The up state insertion loss is 0.84 dB at 30 GHz and 1.75 dB at 40 GHz. The return loss is greater than 10 dB from 0-40 GHz range The measured results demonstrate a phase shift of 286° at 36 GHz with the actuation voltage of 25 V and a return loss better than 10 dB over 0–40 GHz band. Figure 2.26 shows the SEM Image of the (a) entire structure (b) and the cross section.

Fig. 2.26: SEM Image of the (a) fabricated phase shifter structure and (b) cross section of the Membrane [95].

Based on the RF MEMS exhaustive literature survey a summary of RF MEMS phase shifters developed by various researchers in different frequency bands with details such as types of configurations, insertion loss, and number of bits, design topology, phase accuracy and the chip area is presented in Table 2.1.

It is evident from above literature survey that there is lack of systematic study in 5-bit phase shifter in Ku band which is very strategic requirement for defense application. Therefore, there is a need to develop high resolution ( $\geq 5$  bits) Ku- band MEMS based phase shifter, which we undertake in this work.

**Table 2.1: Comparison of RF MEMS Phase Shifters Performance of Different Groups**

| No. of bits | Insertion<br>loss            | Design Type / Substrate                                                                                                                                                                                                 | Phase<br>Accuracy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Chip<br>Area                         | Reference                                   |

|-------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------|

| 2           | 0.65dB                       | Reflect Line<br>500 μm                                                                                                                                                                                                  | ± 11 deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50 mm <sup>2</sup>                   | [78]                                        |

| 4           | 1.15dB                       | Reflect Line<br>500 μm                                                                                                                                                                                                  | ± 11 deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100 mm <sup>2</sup>                  | [78]                                        |

| 4           | 2.25dB                       | Switched Line                                                                                                                                                                                                           | 13 deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50 mm <sup>2</sup>                   | [79]                                        |

| 2           | 0.85 dB                      | Switched Line 200 µm GaAs                                                                                                                                                                                               | ±2deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 12 mm <sup>2</sup>                   | [80]                                        |

| 4           | 1.6 dB                       | Switched Line<br>200 µm GaAs                                                                                                                                                                                            | ± 4 deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 21.3 mm <sup>2</sup>                 | [81]                                        |

| 3           | 2.2dB<br>@ 35 GHz            | Switched Line 75 µm GaAs                                                                                                                                                                                                | ± 6 deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 16 mm <sup>2</sup>                   | [82]                                        |

| 4           | 2.6dB                        | TTD                                                                                                                                                                                                                     | ± 4 deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8.4 mm(L)                            | [83-84]                                     |

| 5           | 3.6dB                        | Switched line<br>200 µm HRS                                                                                                                                                                                             | < 5 deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 28mm <sup>2</sup>                    | [85]                                        |

| 5           | 3.5dB                        | Switched line<br>200 µm HRS                                                                                                                                                                                             | < 2 deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20.8mm <sup>2</sup>                  | [86-87]                                     |

| 3           | 2 dB                         | loaded line                                                                                                                                                                                                             | ±2deg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25 mm <sup>2</sup>                   | [89]                                        |

| 4           | 2 dB                         | loaded line /                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55 mm <sup>2</sup>                   | [90]                                        |

| 4           | 0.96                         | switched line                                                                                                                                                                                                           | 3.96°                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66.78 mm <sup>2</sup>                | [91]                                        |

|             | bits  2  4  2  4  5  5  3  4 | bits     loss       2     0.65dB       4     1.15dB       4     2.25dB       2     0.85 dB       4     1.6 dB       3     2.2dB       4     2.6dB       5     3.6dB       5     3.5dB       3     2 dB       4     2 dB | bits     loss     / Substrate       2     0.65dB     Reflect Line       500 μm     Reflect Line       4     1.15dB     Reflect Line       500 μm     Switched Line       2     0.85 dB     Switched Line       200 μm GaAs     Switched Line       3     2.2dB     Switched Line       3     2.2dB     Switched Line       75 μm GaAs       4     2.6dB     TTD       5     3.6dB     Switched line       200 μm HRS       5     3.5dB     200 μm HRS       3     2 dB     loaded line       4     2 dB     loaded line       4     2 dB     switched line       3     2 dB     loaded line       4     2 dB     switched line | Dits   Loss   / Substrate   Accuracy | Dits   Loss   / Substrate   Accuracy   Area |

\*\*\*\*

# **CHAPTER 3**

# RF MEMS Switch Design Configurations & Simulation Results

There are various design configurations reported in the literature for the capacitive shunt and ohmic series type of switches. The goal of this chapter is to evolve a design configuration which has the built in reliability by optimizing the various features to ensure stable operation of the switches [96-98]. The complete details of design and simulation results are presented in the following sections.

# 3.1 Design Topology for built-in reliability of different Configurations

A split beam concept has been evolved uniquely in comparison to the holes commonly available in the literature. This has been implemented to overcome the various criticalities of restoration force for stable operation and the advantage of the structure release due to large split area during the release process. In fact, it has been emphasised to achieve the higher spring constant with lower structural stress arising due to the structure design. A complete analysis of the spring constant and the stress was carried out to address the long term operation.

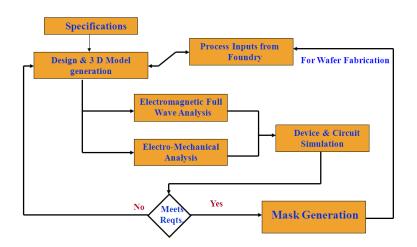

#### 3.1.1 Design Flow

The design flow as shown in the Fig. 3.1 has been evolved for the development of the both type of RF MEMS switches under this work. It begins with the goals for the electrical

and mechanical specifications. Process inputs from the foundry in terms of process capabilities like metallization method and thickness, sacrificial layer characteristics, bridge deposition procedure and release process are taken into account during the design and modelling. After the model generation, the full wave electromagnetic and electro-mechanical analysis has been performed leading to the circuit level simulation. The decision for mask generation shows the confirmation of meeting the requirement specifications. The fabrication of structures and the devices is followed by the mask generation. A simplified cross sectional view and electrical schematic of capacitive shunt and ohmic series switch are shown in Figs. 3.2 (a, b) and 3.3 (a, b) respectively.

Fig. 3.1: Flow for Design, Simulation and Device Development

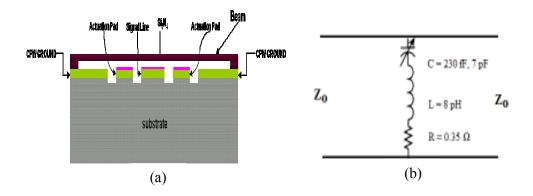

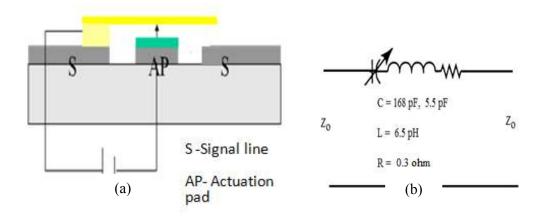

Fig. 3.2: (a) Cross section for shunt capacitive switch and (b) electrical equivalent.

In case of shunt configuration, the electro statically actuated switch consists of a conductive fixed-fixed beam supported by the anchors between the two sections of ground in a coplanar waveguide (CPW) [99]. In this case, parasitic capacitance limits the performance when the switch is in the up state by the unwanted reflections. In order to isolate the dc control voltage from the RF, this design uses separate electrodes for the actuation of the membrane. The bridge can be brought close to the conducting line by the application of sufficient bias voltage through the actuation electrodes. For simple structures this is determined by making use of the force balance equations between the electrostatic pull down and mechanical restoring forces on the bridge.

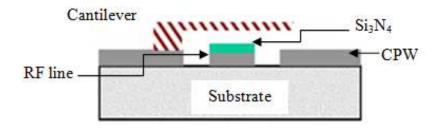

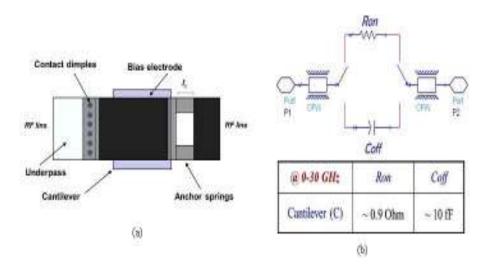

The series switch [100] is developed as shown in Fig. 3(a) for the cross sectional view with cantilever having the anchor pad on the one side of the transmission line and discontinuity in the RF line. The actuation pad is covered with the silicon nitride dielectric to avoid the direct contact of the RF and actuation potential. This avoids the hard contact of the actuated cantilever with the dc electrode. The MEMS cantilever is modelled by a series capacitor-inductor-resistor combination as shown in the Fig. 3.3 (b). The values shown for the capacitor, inductor and the resistance have been extracted for the model used for the development.

Fig. 3.3: (a) Cross section for ohmic series switch and (b) electrical equivalent.

# 3.2 Design topology and Simulation

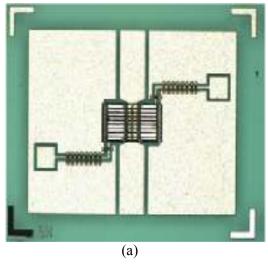

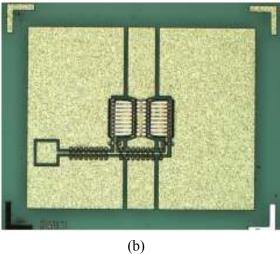

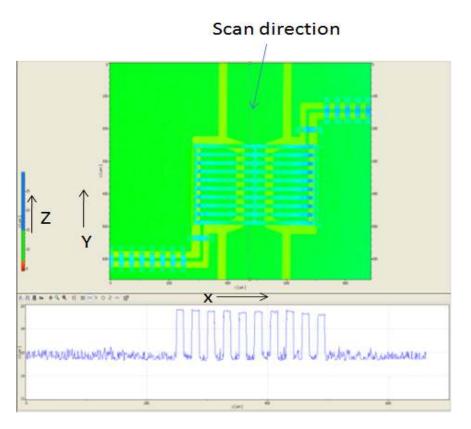

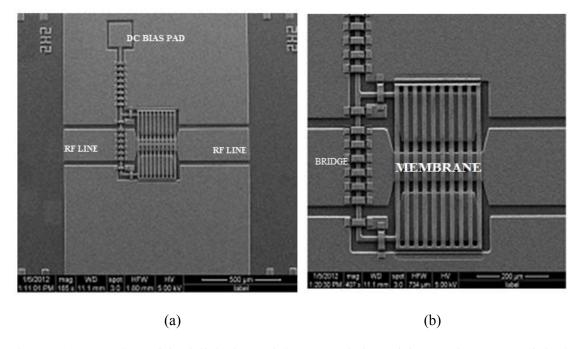

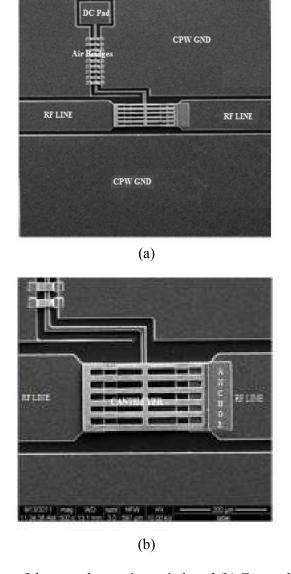

#### 3.2.1 Split Beam Capacitive Shunt Configuration

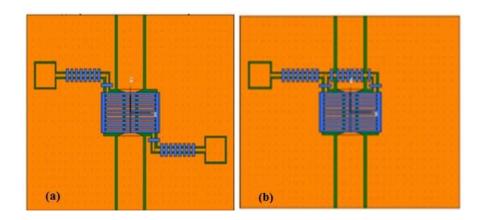

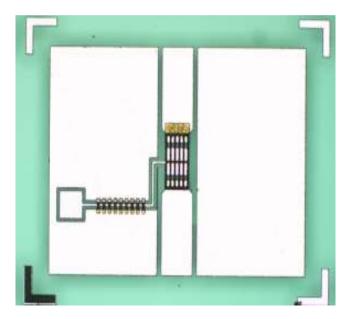

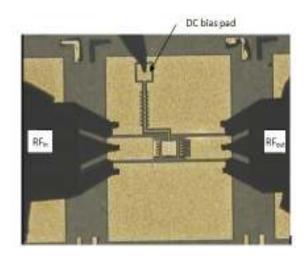

The primary emphasis of this work was to design the capacitive shunt MEMS switch configuration with split membranes for low force with electrostatic actuation and sufficient restoration force. Two configurations i.e. having DC bias pads on both sides and only one side were designed. Both these configurations have been provided the symmetric actuation along the RF line for uniform pull in. The configuration having single bias pad was conceived for simple implementation of the switch in the systems during practical application. Single bias pad has lot of ease in applying the DC potential in comparison to the two bias pad configurations however this needed to create a discontinuity in the RF line. The discontinuity has been provided in the single DC bias pad design in view to study its effects on RF performance. The RF line is connected through the air bridges over the DC line. All other design parameters have been exactly same in both the configurations. Both the configurations have bias pad on the periphery so that smaller length of bond wire is sufficient during assembly and packaging to avoid the parasitic effects at high frequencies. Fig. 3.4 (a) and (b) shows the top view of both the configurations. The CPW of 50Ω impedance with Ground/Signal/Ground (GSG) configuration was used for design.

Fig. 3.4: (a) Top view of the two side dc bias pad and (b) single dc bias pad.

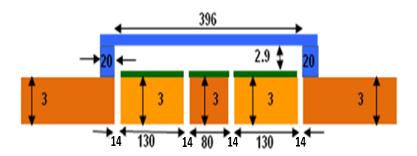

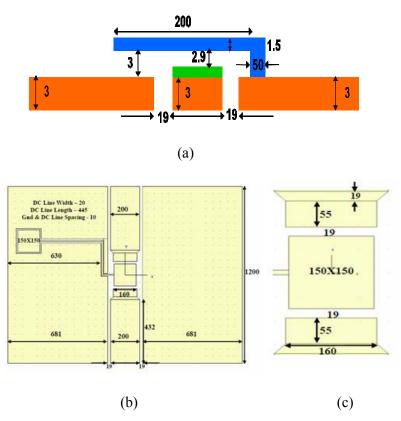

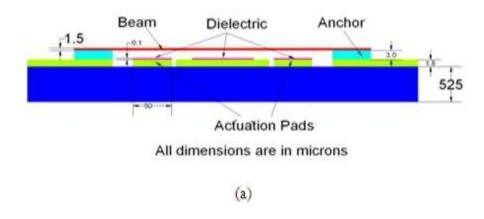

Figure 3.5 shows the cross section of the shunt switch displaying all the dimensions of the beam and actuation area. The actuation pads have 130 x 250  $\mu$ m<sup>2</sup> area. The thickness of the CPW and actuation electrodes is 3.0  $\mu$ m. The actuation electrode and RF line has been deposited with 0.1  $\mu$ m silicon nitride. The anchors have foot print area 20x20  $\mu$ m<sup>2</sup> area. The beam length is 436  $\mu$ m including anchors.

Fig. 3.5: Cross section of beam area with actuation pad. All dimensions are in μm.

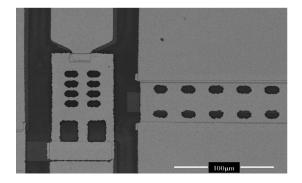

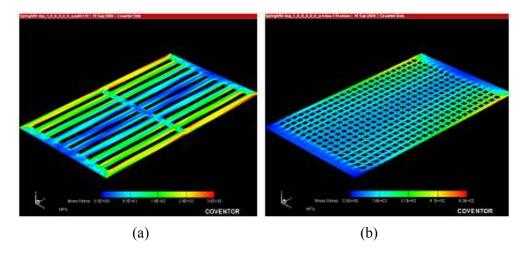

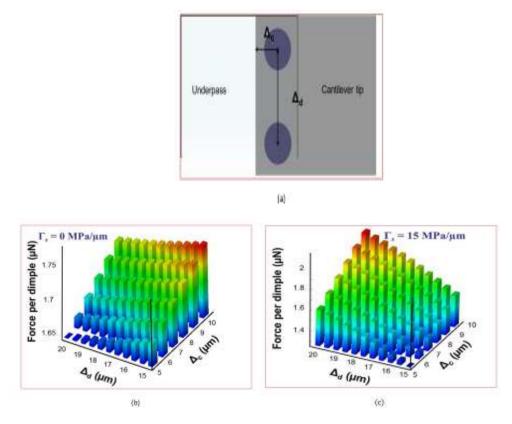

The split beams in rectangular shape instead of holes from other reported work has the advantage of low stress across the beam making it more robust to the environmental effects like vibration and shock. The other advantage is the ease in structure release due to continuous larger area available for etchant percolation. Figure 3.6 (a) and (b) shows the 3D models of the split beam and rectangular holes analyzed with FEM for stress analysis. The Beam outer dimensions have been taken as same for both the configurations except for the internal structural design. The mass of the beam structure also has been maintained same for both the configurations so as to analyze the proposed split beam structure with respect to the rectangular holes structure. The holes dimension is  $10x10~\mu\text{m}^2$  and the edge to edge gap between the holes has been optimized in order to achieve the same mass as of the split beam structure.

The membrane details with respect to dimension and gap are given in the Table 3.1. The analysis shows that the stress of the order 630 MPa in case of rectangular holes and 380 MPa for the split beam configuration has been observed. The stress analysis shows the

superiority of split beam design with respect to the rectangular holes. CoventorWare has been used for the simulation and analysis.

Fig.3.6: (a) and (b) Stress analysis 3D models for the split and rectangular holes beam respectively.

Table 3.1: Dimensional details for the membrane

| Beam Details                             | Parameters                |                       |  |

|------------------------------------------|---------------------------|-----------------------|--|

| Dimensions(μm)                           | Length :396<br>Width: 249 | Thickness 1.5         |  |

| Туре                                     | Split                     | Rectangular holes     |  |

| Stress (MPa)                             | 380                       | 630                   |  |

| Stress<br>Area between split beams/holes | 178 x11 μm²               | 10x10 μm <sup>2</sup> |  |

| Array size                               | 9x2                       | 22x16                 |  |

For the proposed structure, the 3D full wave electromagnetic simulation was carried out by a finite element method using Ansoft HFSS. Figure 3.7 shows the effective length of the membrane and the points at which pull in force is applied due to underneath placement of actuation electrodes on both sides for symmetric actuation. The effective beam has length of

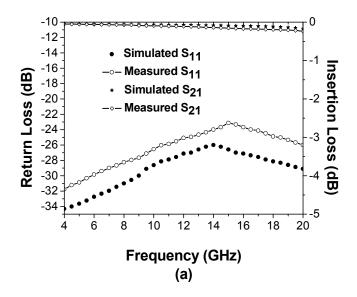

396μm. The EM simulation results of RF parameters such as isolation, return and insertion loss are shown in comparison to the measured results in the the experimental section.

Fig. 3.7: Dimensions for the reduced model excluding anchors.

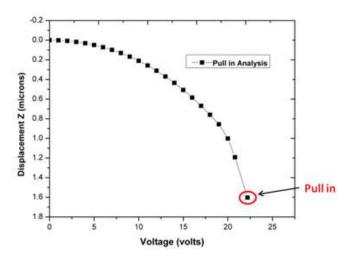

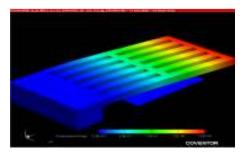

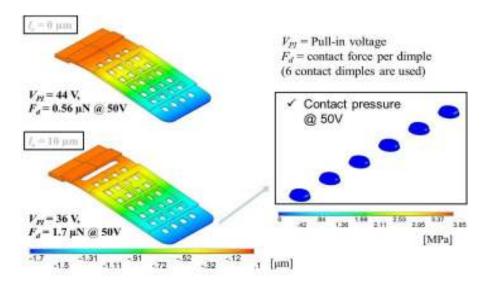

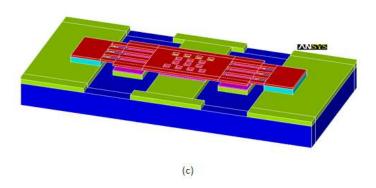

#### 3.2.2 Electromechanical Simulation Results

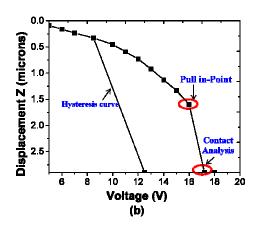

A 3D model in CoventorWare is generated using customized process. Device fabrication method was implemented for the structure feasibility. A 2D layout was generated for each and every mask pertaining to the fabrication steps of the device. Finally both, the fabrication flow and 2D mask layouts were integrated to generate the 3D model of the device. The analysis has been done through finite element method using manhattan meshing and the beam was fixed at the extreme ends. Further the membrane was allowed to deform with respect to the application of gradual increase in voltage. The electromechanical simulation result for the pull in voltage is shown in the Fig. 3.8.

Fig. 3.8: Voltage versus displacement curve for pull-in.

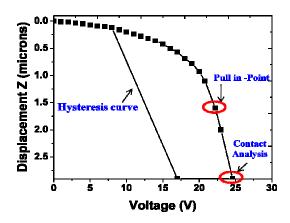

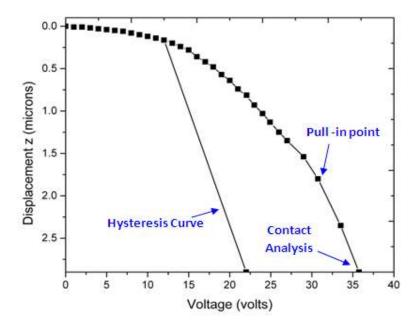

A nearly linear deflection has been obtained for a travel of 1.6µm at a voltage of 22.2V up to the pull in point. Beyond the pull in voltage point a sudden snap down was observed. The membrane was analyzed for the hysteresis response which is quite crucial for the stable operation of the switch. Figure 3.9 shows the contact point at the 24.3V having air gap as 2.9µm. The pull back phenomenon also called restoration force, occurred at the 17V after removal of the actuation potential. The pull back shows that the design has the sufficient restoration force required for the stable operation of the device.

The membrane was split into ten strips each having width of  $15\mu m$  and gap of  $11\mu m$ . This was optimized keeping in view the air damping and the easy removal of the sacrificial layer during the fabrication of MEMS switches.

Fig. 3.9: Contact and Hysteresis analysis curve.

The pull in voltage was calculated using the equation (1)

$$V_p = \sqrt{\frac{8k d^3}{27 \, sA}} \tag{1}$$

Where k = Spring Constant

$d = gap between electrodes = 2.9 \mu m$

A = Area of electrode

$\varepsilon$  = permittivity of air

Spring constant has been calculated using equation (2) for the membrane

$$k = 16EW\left(\frac{t}{l}\right)^3\tag{2}$$

Where  $t = \text{Thickness of membrane} = 1.5 \, \mu \text{m}$

E= Young's Modulus = 79 GPa

W = width of the beam

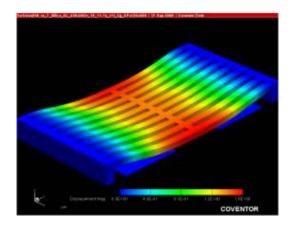

Based on the model values used in equation (2) the spring constant was found to 17.17 N/m for the fixed-fixed beam. This value was inserted in equation (1) and the pull in voltage was calculated as 20.76V. By simulation the pull in voltage was found to be 22.2V. A 3D view of the Membrane deflection is shown in the Fig. 3.10. The maximum deflection has been observed at the centre of the membrane which is required for the proper contact at the centre of the transmission line.

Fig. 3.10: A 3D model of beam under pull-in and contact analysis.

The mechanical resonance is significant from the structural integrity point of view. Membrane was split into smaller widths with uniform air gap between the split membranes. This has helped to increase the mechanical resonant frequency and to minimize the effects of squeeze film damping. The membrane was subjected to modal analysis to estimate the resonant frequency so as to analyze the effect of vibrations when implemented in field

applications. The results are shown in the Table 3.2 for the six modes. The structural resonance of the first mode was found to be 16.84 KHz through the modal analysis. This value is quite satisfactory in response to the environmental effects this could face in the field applications. The natural frequency above 2000Hz ensures its reliable operation as per military standards.

TABLE 3.2: Modal Analysis for Resonance Frequency

|      | Frequency | Mode Mass              |  |

|------|-----------|------------------------|--|

| Mode | (KHz)     | (kg.)                  |  |

| 1    | 16.84     | 6.95x10 <sup>-10</sup> |  |

| 2    | 22.46     | 3.12x10 <sup>-10</sup> |  |

| 3    | 37.38     | 3.31x10 <sup>-10</sup> |  |

| 4    | 47.69     | 7.47x10 <sup>-10</sup> |  |

| 5    | 50.13     | 3.80x10 <sup>-10</sup> |  |

| 6    | 55.22     | 4.15x10 <sup>-10</sup> |  |

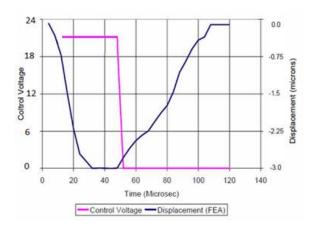

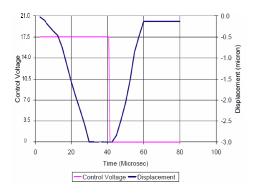

The dynamic response was carried out using Intellisuite finite element analysis. The switching time can be computed by the equation (3). It has been observed that by keeping more gaps between the strips, membrane response time can be improved.

$$t_s \cong 3.67 \frac{V_p}{V_s} \frac{1}{2\pi f o} \tag{3}$$

Whereas  $V_p$  is the pull in voltage,  $V_s$  is the source voltage and  $f_o$  is the resonant frequency. From the simulation ON-time (downward transition) is  $32\mu$ sec and OFF-time (upward) transition was found to be  $48\mu$ sec as shown in the Fig. 3.11. A potential little over pull-in was applied to switch on the device.

Fig. 3.11: Transition analysis for ON/ OFF time.

# 3.3 Layout Details

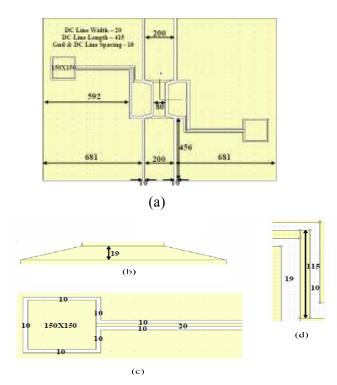

# 3.3.1 Double bias pad Configuration

Figure 3.12 (a) shows the detailed dimensions of the first metal layer layout. Figs. 3.12 (b), (c) and (d) show the details of tapered transition, bias pad and the DC line with gaps with respect to the ground.

Fig. 3.12: (a) Full view with dimensions, (b) Tapering, (c) Bias pad and (d) DC Line.

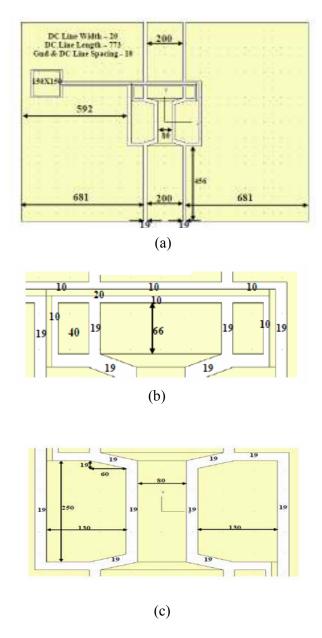

#### 3.3.2 Single bias pad Configuration

Figure 3.13 (a) shows the detailed dimensions of the first metal layer layout. The Figures 3.13 (b) shows the details of the RF line with DC bias pad with gaps with respect to the ground where as Figure 3.13 (c) shows the detailed dimensions of the electrodes which are common for both the configurations.

Fig. 3.13: (a) Full view with dimensions, (b) RF line with discontinuity for dc bias provision and (c) electrodes view with dimensions (common for both configurations).

# 3.4 Simulation Results

The Summary of simulation results for both capacitive type configurations are depicted in the Table 3.3. The simulation results in the frequency range of 4-20GHz have shown a small degradation in the insertion loss and return loss for the double DC bias pad in comparison to the single DC bias pad. The simulation and pull back voltage are same as the mechanical dimensions are exactly same for both the configurations.

Table 3.3: Simulation Results – Split Beam Capacitive Shunt Switch

| Parameters                        | Units   | Single DC bias pad |             | Two DC bias pads |             |

|-----------------------------------|---------|--------------------|-------------|------------------|-------------|

| Frequency                         | [GHz]   | 4-20               |             | 4-20             |             |

| requency                          | [OIIZ]  | Down<br>State      | UP<br>State | Down<br>State    | UP<br>State |

| Insertion Loss (S <sub>21</sub> ) | [dB]    | < - 40.10          | > - 0.20    | < - 42.8         | > -0.15     |

| Returns Loss (S <sub>11</sub> )   | [dB]    | > - 0.6            | < - 26.0    | <- 0.7           | < - 29.2    |

| Pull-in Voltage                   | [Volts] | olts] ≈ 22.2       |             |                  |             |

| Pull back at                      | [Volts] | ≈ 17.1             |             |                  |             |

# 3.5 Ohmic Series Configuration

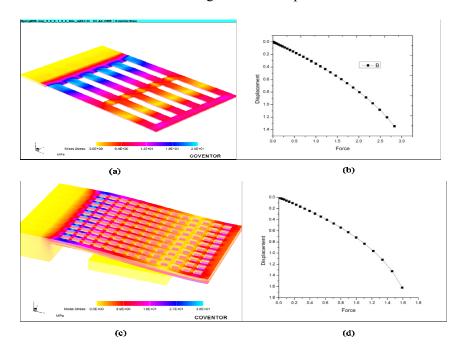

The design of ohmic series switch was also done using split beams in rectangular shape instead of holes from other reported work. This configuration also in comparison to the rectangular holes has the advantage of low stress at the anchor junction, higher spring constant and higher mechanical resonant frequency making it more robust to the environmental effects and ease in structure release due to continuous larger gap for etchant percolation. Figure 3.14 (a) and (c) shows the 3D models of the split cantilever and rectangular holes analysed with FEM for stress analysis. The cantilever outer dimensions have been taken as same for both the configurations except for the internal structural design.

Fig. 3.14: (a) and (c) Stress analysis whereas (b) and (d) shows the force versus displacement curve for split and rectangular holes cantilever respectively.

The results show the low stress levels and higher linearity of the split cantilever configuration in comparison to the conventional rectangular holes concept. The units of the displacement and force shown are in  $\mu m$  and  $\mu N$ . The mass of the cantilever structure has

been maintained same for both the configurations so as to analyse the proposed split structure with respect to the rectangular holes structure. The holes dimension is  $10x10~\mu\text{m}^2$  and the edge to edge gap between the holes has been optimized in order to achieve the same mass as of the split beam structure. The split cantilever details are given subsequently. The analysis shows that the stress of the order 36 MPa in case of rectangular holes and 26 MPa for the split beam configuration has been observed. The stress analysis shows the superiority of split cantilever design with respect to the rectangular holes.

Figure 3.15(b) and (d) shows the force versus displacement graphs for these two configurations redrawn from the displacement versus voltage data of the CoventorWare finite element analysis using equation 4.

$$F = \frac{\varepsilon A V^2}{2g^2} \tag{4}$$

Where A =Area of electrode

$g = \text{gap between electrodes}, 2.9 \,\mu\text{m}$

$\varepsilon$  = permittivity of air

V = applied voltage

The spring constant was derived using the slope of force versus displacement graphs at different points in the linear region using equation (5). The derived values of k have been found to be 2.86 N/m and 1.39 N/m for split beam and rectangular holes respectively clearly showing the advantage of split beam configuration in terms of superior spring constant.

$$F = k\delta x \tag{5}$$

Where

k = Stiffness

x = displacement

The above analysis clearly demonstrates the superiority of the split beam cantilever structure to the rectangular holes in terms of numerous parameters responsible for realization and the stable operation. Figure 3.15 (a) shows the cross sectional view of the ohmic series

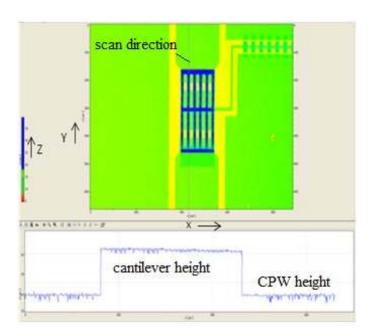

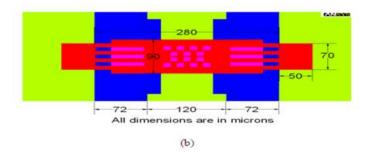

having cantilever. The CPW of  $50\Omega$  impedance with Ground/Signal/Ground (GSG) configuration was used for design. The G/S/G dimensions for the CPW configuration are  $19/200/19~\mu m$ . The air gap of  $3.0\mu m$  was maintained for this design also, so as to process these in the same mask having same fabrication process. The actuation electrode was provided with the  $Si_3N_4$  dielectric which makes this configuration less prone to stiction issues arising due to micro welding effects [101]. The CPW metal thickness was taken as  $3.0\mu m$  for this design. In this structure, the 3D full wave electromagnetic simulation was carried out by a finite element method using Ansoft HFSS. The EM simulation results of RF parameters are shown in comparison to the measured results in the experimental results and discussion section. The cantilever was split into six strips each having width of  $15\mu m$  and gap of  $12\mu m$ .

Fig. 3.15: (a) Cross section for cantilever having actuation electrode, (b) and (c) shows the details of the first metal layer and of the actuation electrode respectively. All dimensions shown in figures are in µm.

This was done keeping in view minimizing the effects of air damping and the easy removal of the sacrificial layer during the fabrication of MEMS switches. The pull in voltage was calculated using equation (1). Spring constant has been calculated using equation (6)

$$k = \frac{2\left(\frac{E}{1-v^2}\right)wt^3}{3l^3} \tag{6}$$

Where  $t = Thickness of membrane = 1.5 \mu m$

E = Young's Modulus = 79 GPa

W= width of the beam

v = poisson's ratio

Fig. 3.16: 3D model of Cantilever under pull in analysis.

A 3D view of the cantilever under electrostatic simulation is shown in the Fig. 3.16 displaying maximum deflection at the edge of the cantilever. Based on the model values used in equation (6), the spring constant was found to be 4.04 N/m for the cantilever. These values were used in equation (1) and the pull in voltage was calculated as 12.53V. By simulation the pull in voltage is found to be 15.8V. Beyond the pull in voltage point a sudden snap down was observed and analyzed under contact and hysteresis analysis. The cantilever was analyzed for the hysteresis response which is quite crucial for the smooth operation of the switch. Figure 3.17 shows the contact analysis and hysteresis curve after removal of the DC bias from the actuation electrodes and the cantilever comes back to its original position under force of spring constant at 12.6V for air gap of 3.0μm. The simulations were carried out using

FEM model of the switch. The hysteresis curve shows the pull back of the cantilever after removal of the actuation voltage.

Fig. 3.17: Contact Analysis and Hysteresis curve.

The cantilever was subjected to modal analysis using CoventorWare to estimate the resonant frequency so as to analyze the effects of various vibrations when implemented in field applications. Keeping in view the effect of split beam the damping was considered zero during simulation. The structural resonance frequency was found to be 11.199 KHz. The value is quite satisfactory in response to the environmental effects this could face in the field applications. Table 3.4 shows the values of the resonance frequency of the first six modes.

Table 3.4: Modal Analysis frequency for Cantilever

| Mode | Frequency (KHz) | Mass (kg.)             |

|------|-----------------|------------------------|

| 1    | 11.199          | 1.73x10 <sup>-11</sup> |

| 2    | 41.908          | 1.10x10 <sup>-11</sup> |

| 3    | 64.125          | 1.93x10 <sup>-11</sup> |

| 4    | 132.803         | 9.60x10 <sup>-12</sup> |

| 5    | 141.402         | 1.04x10 <sup>-11</sup> |

| 6    | 185.063         | 2.14x10 <sup>-11</sup> |

The dynamic response of the switch was carried out using Intellisuite finite element analysis. The cantilever was split into smaller width with air gap in between the strips to improve the time response of the switch. The switching time can be computed by the equation (8). It has been observed that by keeping more gap between the strips time response can be improved. Whereas  $V_p$  is the pull in voltage,  $V_s$  is the source voltage and  $f_o$  is the resonant frequency. From the simulation ON-time (downward transition) is 21 µsec and OFF-time (upward) transition was found to be 19µsec for the switch as shown in the Fig.3.18. A potential of 21.0V was applied to switch on the device.

Fig. 3.18: Switch Transition analysis for on / off time.

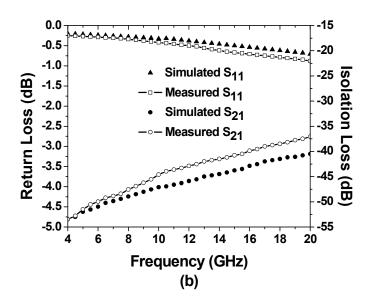

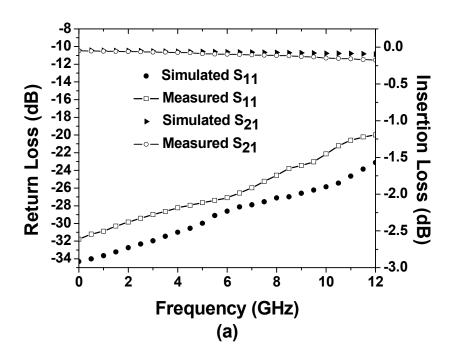

#### 3.5.1 Simulation Results

The simulation shows the insertion loss as 0.15dB and return loss better than 22.7dB for this configuration at 17.1V of pull in voltage.

Table 3.5: Summary Simulation Results – Ohmic Series Switch

| Parameters                        | Units   | Split beam Cantilever |           |  |

|-----------------------------------|---------|-----------------------|-----------|--|

| Fraguanov                         | [GHz]   | DC – 12 GHz           |           |  |

| Frequency                         |         | ON State              | OFF State |  |

| Insertion Loss (S <sub>21</sub> ) | [dB]    | < - 0.15              | < - 45.2  |  |

| Returns Loss (S <sub>11</sub> )   | [dB]    | > - 22.7              | < - 0.5   |  |

| Pull-in Voltage                   | [Volts] | ≈ 17.1                |           |  |

| Pull back at                      | [Volts] | ≈ 13.4                |           |  |

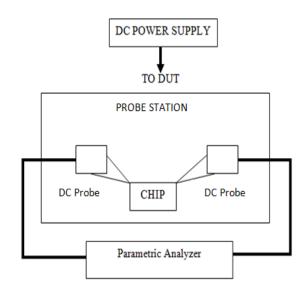

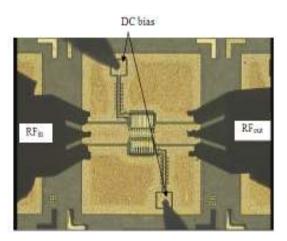

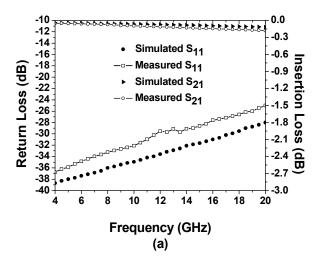

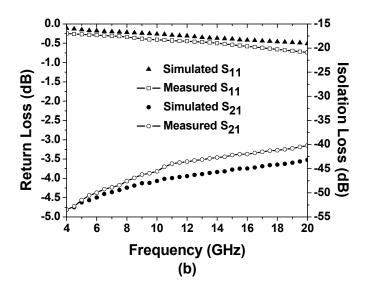

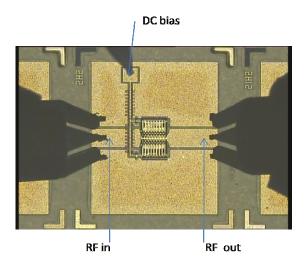

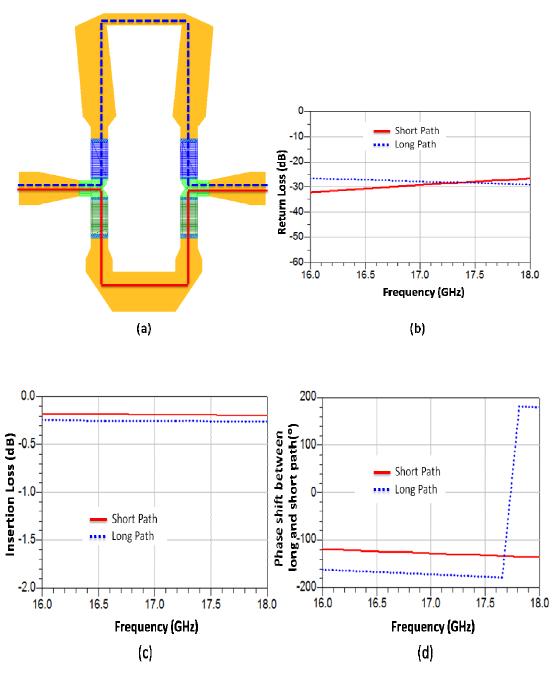

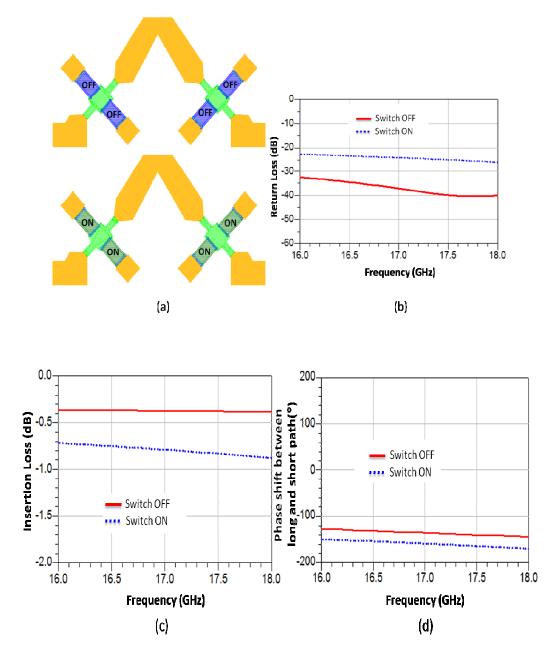

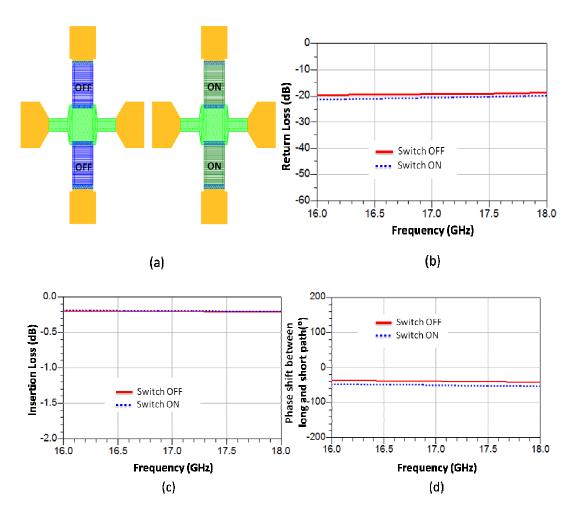

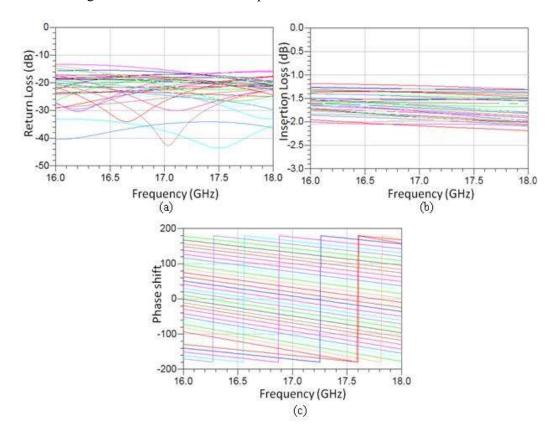

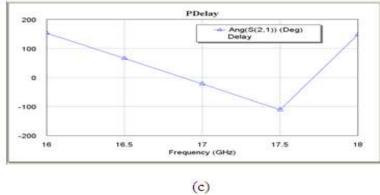

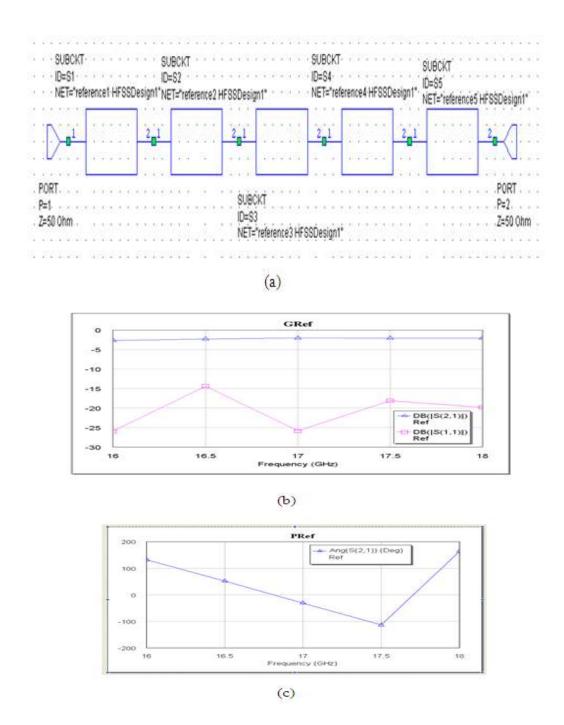

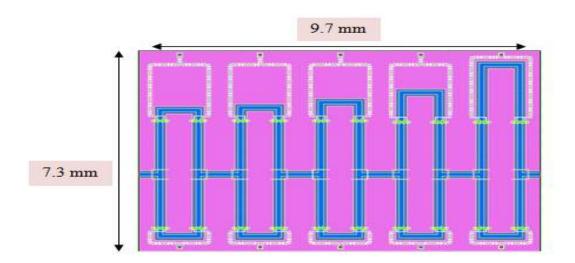

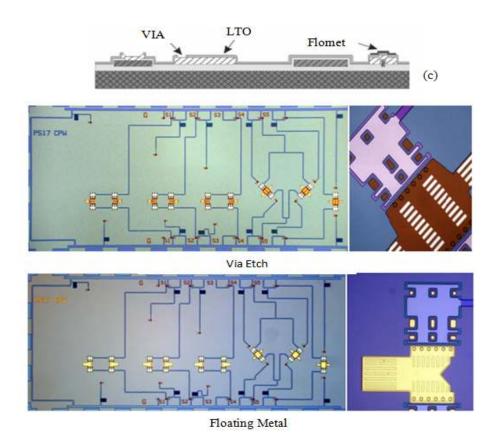

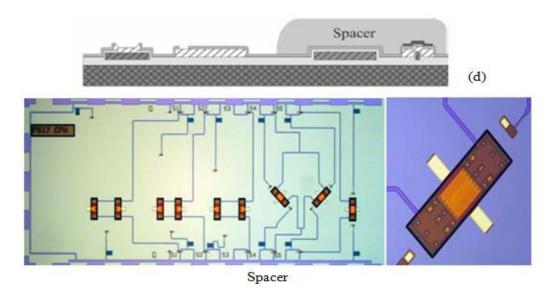

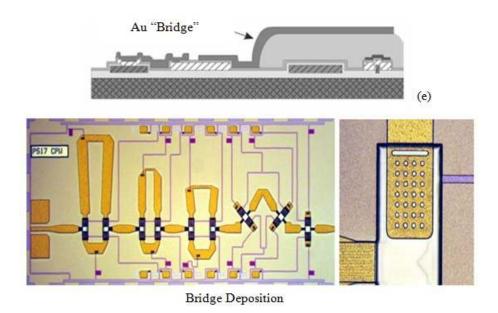

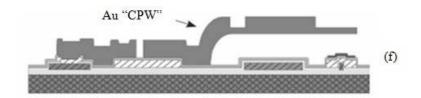

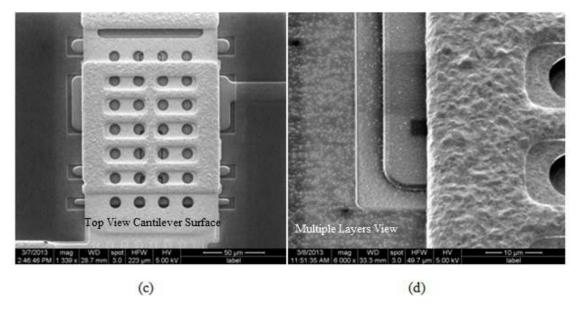

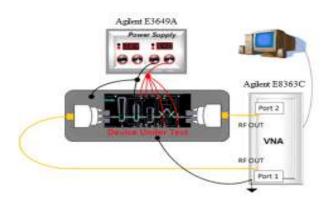

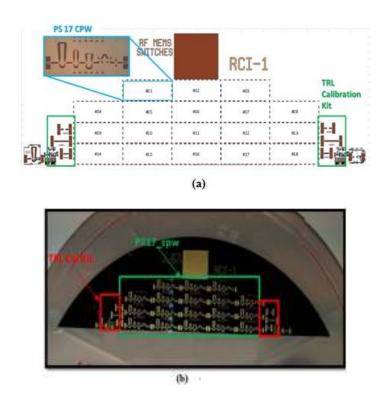

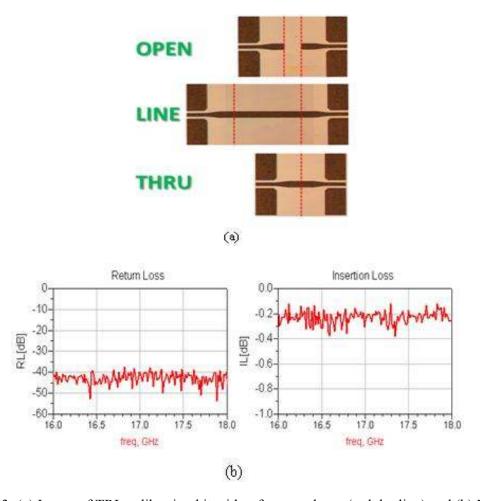

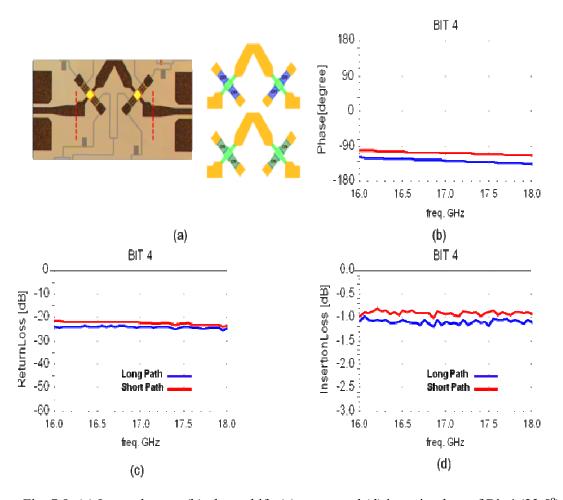

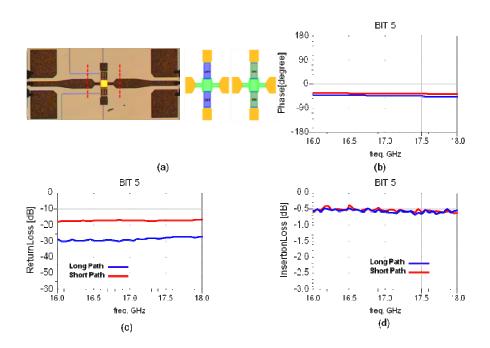

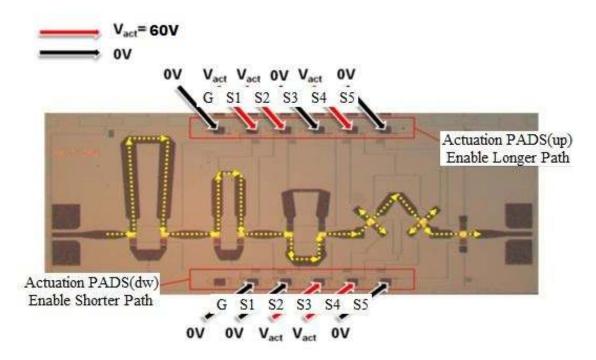

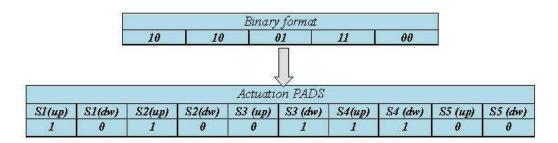

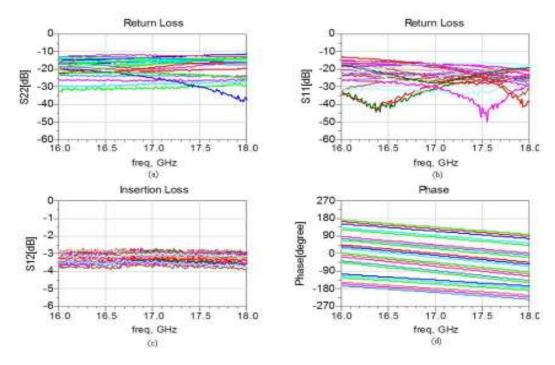

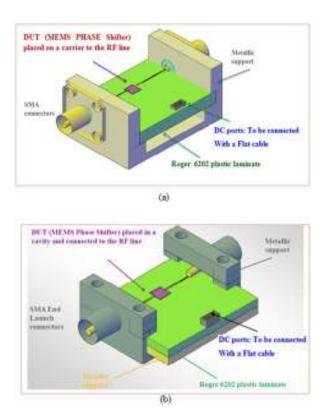

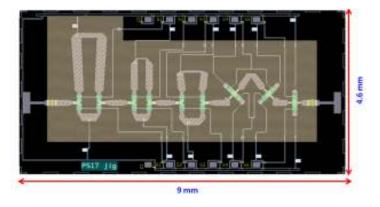

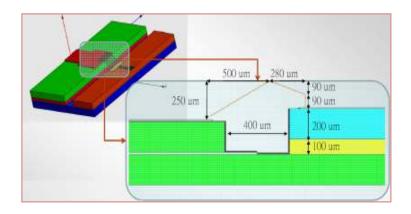

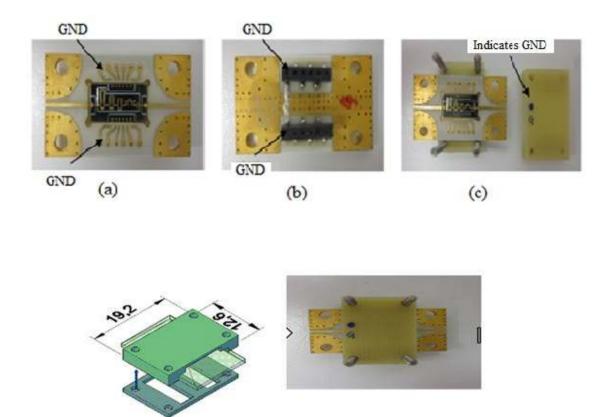

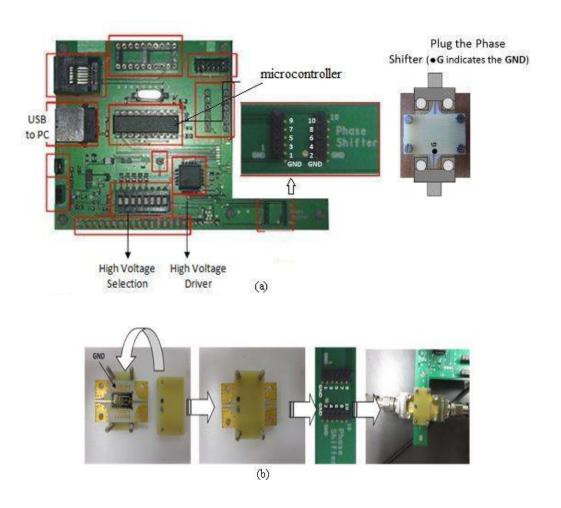

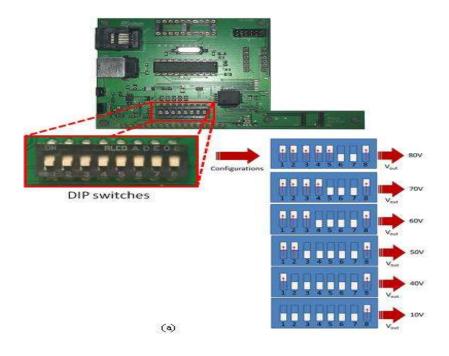

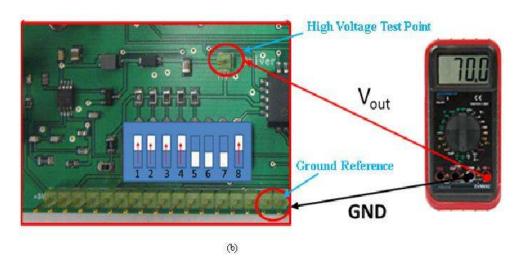

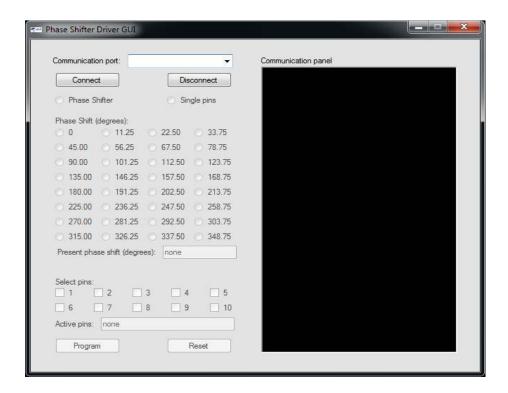

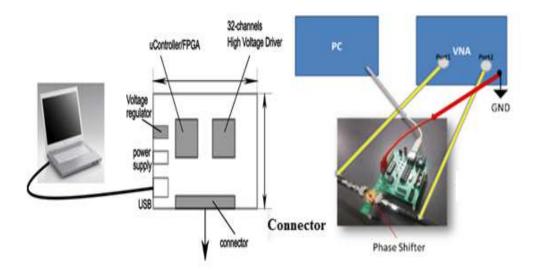

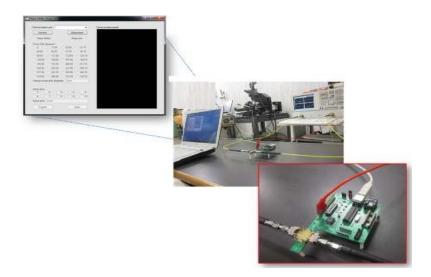

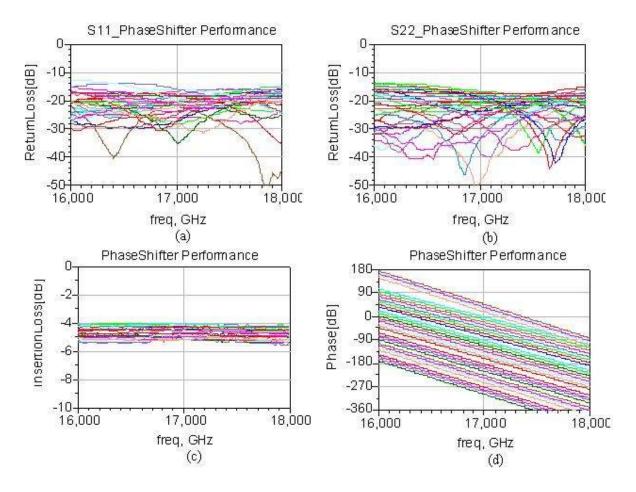

# **Summary**