# HIGH PERFORMANCE CMOS WIDE-BAND RF FRONT-END WITH SUBTHRESHOLD OUT OF BAND SENSING

Nisha Gupta

A Thesis Submitted to Indian Institute of Technology Hyderabad In Partial Fulfillment of the Requirements for The Degree of Doctor of Philosophy

Department of Electrical Engineering

December 2017

© Copyright by Nisha Gupta, 2018. All Rights Reserved

### Declaration

I declare that this written submission represents my ideas in my own words, and where ideas or words of others have been included, I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be a cause for disciplinary action by the Institute and can also evoke penal action from the sources that have thus not been properly cited, or from whom proper permission has not been taken when needed.

### **Approval Sheet**

This thesis entitled "HIGH PERFORMANCE CMOS WIDE-BAND RF FRONT-END WITH SUBTHRESHOLD OUT OF BAND SENSING" by Nisha Gupta (EE12P0001) is approved for the degree of Doctor of Philosophy from IIT Hyderabad.

Dr. Maryam Shojaei, IIT Bombay

Examiner 1

Dr. Amit Patra, IIT Kharagpur

Examiner 2

Dr. Amit Acharyya

Internal Examiner

Dr. Ashudeb Dutta

Adviser/Guide

Dr. Shiv Govind Singh

Co-Adviser

Dr. Sobhan Babu

Chairman

### Acknowledgements

Even though I am the author of this thesis, several others also helped me to complete this work in a very successful way. It is my duty to thank and mention them here.

First of all, I take immense pleasure in displaying my eternal gratitude towards my teacher, guide and advisor Prof. Ashudeb Dutta for having shown perpetual interest towards my research growth. Being the student in the Electrical department, in the absence of his constant technical support and moral motivations I could not have overcome all the hurdles throughout my academic career development. I never failed to admire him for his never give-up determination and am thankful to my fullest heart for all the technical and moral advices that he has been endorsing me with, which made me to evolve in multiple perspectives.

I would like to thank my Co-guide Prof. Shiv Govind Singh for having shown equivalent interest in my research works. I must thank him for his right help in the right places at right moments, without which my research path would have not been fulfilled. I also feel happy to mention my thesis committee members Prof. amit acharyya, Prof Siva Rama Krishna Vanjari, Prof. K Sri Rama Murthy and Prof. Shobhan babu who have been pointing out even the smallest areas where I need to improve and have carefully sculptured my thesis path in an organized way. Apart from it i want to thanks Prof. Gajendranath Chowdary.

I also offer my sincere gratitude to few great people who helped me at different levels of my research work. I must also thank, Sc. M. Madhav Kumar (ANURAG-DRDO) for his worthily discussions during the design and layout phases of my work. I whole heartily thank Dr. Bhibu Dutta Sahoo (Amrita Vishwa Vidyapeetham, Kerala) for his profound contribution in my research with great patience and passion, and for helping me to perceive analog RF design from an entirely different angle which divulged my vision towards my domain in many folds.

I also thank Mr.P. Sarkar, Mr. V. S. Rao, Mr. Yoganandha Varma and their team (Alpha pvt Ltd., Hyderabad) SPEL semiconductor, Si2Microsystem and IMEC, Belgium (Europractice) for their complete support in various designing parts of my chips. I also thank Mr. V. S. Rao, Mr. Yoganandha Varma and their team (Astra Microwave Products Ltd., Hyderabad) for their complete support during the final testing phase of my work.

I would like to convey my thanks, wishes and regards to my colleagues Mr. AR Aravinth kumar, Ragulagadda Sesha Sai Ram, Pankaj kumar Jha and Mr. Hafeez K T, who have stood by me in almost all my difficulties, struggles and has given strength and motivation from inside to face problems related to all dimensions of life. I feel proud to thank my entire lab members and fellow researchers who indeed served as a second family here at IITH. Their helps always motivated me towards research and makes me feel responsible every time.

I also thank all fellow friends at IITH who made my life at the campus very pleasant. I take this moment to thank all technicians, lab assistants and office staffs of IITH for their timely support whenever I required.

Last but not least, I sincerely thank my parents and all my family members for standing with me in all the difficult decisions that I took with absolute hope and faith at my view towards my research career.

### Dedication

To my dear husband and beloved parents

### Abstract

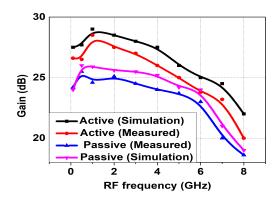

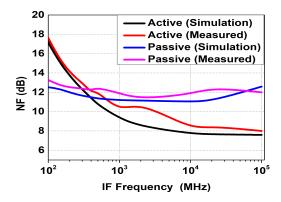

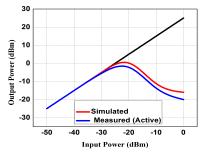

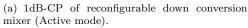

In future, the radar/satellite wireless communication devices must support multiple standards and should be designed in the form of system-on-chip (SoC) so that a significant reduction happen on cost, area, pins, and power etc. However, in such device, the design of a fully on-chip CMOS wideband receiver front-end that can process several radar/satellite signal simultaneously becomes a multifold complex problem. Further, the inherent high-power out-of-band (OB) blockers in radio spectrum will make the receiver more non-linear, even sometimes saturate the receiver. Therefore, the proper blocker rejection techniques need to be incorporated. The primary focus of this research work is the development of a CMOS high-performance low noise wideband receiver architecture with a subthreshold out of band sensing receiver. Further, the various reconfigurable mixer architectures are proposed for performance adaptability of a wideband receiver for incoming standards. Firstly, a high-performance low- noise bandwidthenhanced fully differential receiver is proposed. The receiver composed of a composite transistor pair noise canceled low noise amplifier (LNA), multi-gate-transistor (MGTR) trans-conductor amplifier, and passive switching quad followed by Tow Thomas bi-quad second order filter based tarns-impedance amplifier. An inductive degenerative technique with low-VT CMOS architecture in LNA helps to improve the bandwidth and noise figure of the receiver. The full receiver system is designed in UMC 65nm CMOS technology and measured. The packaged LNA provides a power gain 12dB (including buffer) with a 3dB bandwidth of 0.3G - 3G, noise figure of 1.8 dB having a power consumption of 18.75mW with an active area of 1.2mm\*1mm. The measured receiver shows 37dB gain at 5MHz IF frequency with 1.85dB noise figure and IIP3 of +6dBm, occupies 2mm\*1.2mm area with 44.5mW of power consumption. Secondly, a 3GHz-5GHz auxiliary subthreshold receiver is proposed to estimate the out of blocker power. As a redundant block in the system, the cost and power minimization of the auxiliary receiver are achieved via subthreshold circuit design techniques and implementing the design in higher technology node (180nm CMOS). The packaged auxiliary receiver gives a voltage gain of 20dB gain, the noise figure of 8.9dB noise figure, IIP3 of -10dBm and 2G-5GHz bandwidth with 3.02mW power consumption. As per the knowledge, the measured results of proposed main-high-performancereceiver and auxiliary-subthreshold-receiver are best in state of art design. Finally, the various reconfigurable mixers architectures are proposed to reconfigure the main-receiver performance according to the requirement of the selected communication standard. The down conversion mixers configurability are in the form of active/passive and Input (RF) and output (IF) bandwidth reconfigurability. All designs are simulated in 65nm CMOS technology. To validate the concept, the active/ passive reconfigurable mixer configuration is fabricated and measured. Measured result shows a conversion gain of 29.2 dB and 25.5 dB, noise figure of 7.7 dB and 10.2 dB, IIP3 of -11.9 dBm and 6.5 dBm in active and passive mode respectively. It consumes a power 9.24mW and 9.36mW in passive and active case with a bandwidth of 1 to 5.5 GHz and 0.5 to 5.1 GHz for active/passive case respectively.

# Contents

|   | Dec  | laration | 1         |                                                                   | iii  |

|---|------|----------|-----------|-------------------------------------------------------------------|------|

|   | App  | roval S  | heet      |                                                                   | iv   |

|   | Ack  | nowledg  | gements . |                                                                   | v    |

|   | Abs  | tract .  |           |                                                                   | viii |

| N | omer | ıclatur  | re        |                                                                   | xiv  |

| 1 | Intr | oduct    | ion       |                                                                   | 1    |

|   | 1.1  | Introd   | luction   |                                                                   | 1    |

|   | 1.2  | Aim a    | and Motiv | ration                                                            | 3    |

|   | 1.3  | Highli   | ghts of R | esearch Investigations                                            | 4    |

|   | 1.4  | Overv    | iew of Th | nesis Contribution                                                | 4    |

|   |      | 1.4.1    | Blocker   | Rejection Wireless Receiver Techniques                            | 4    |

|   |      | 1.4.2    | High Pe   | erformance Bandwidth Extension Low Noise Main Path Receiver .     | 5    |

|   |      | 1.4.3    | Auxiliar  | ry Path Ultra low power Out of Band Sensing Subthreshold Receiver | r 6  |

|   |      | 1.4.4    | Reconfig  | gurable Down Conversion Mixer                                     | 7    |

|   |      |          | 1.4.4.1   | Reconfigurable Active/Passive Down conversion mixer for wide-     |      |

|   |      |          |           | band Receiver                                                     | 7    |

|   |      |          | 1.4.4.2   | A Low/High Band Parallel path TCA with configurable (Ac-          |      |

|   |      |          |           | tive/Passive) Down Conversion Mixer                               | 7    |

|   |     |        | 1.4.4.3 Reconfigurable High/Low band Passive Down Conversion mixer |    |

|---|-----|--------|--------------------------------------------------------------------|----|

|   |     |        | for wide band Receiver                                             | 8  |

| 2 | Blo | cker R | ejection Wireless Receiver Techniques                              | 9  |

|   | 2.1 | Introd | luction                                                            | 9  |

|   | 2.2 | Effect | of Blocker on Wideband Receiver                                    | 10 |

|   |     | 2.2.1  | Blocker Impact on Various Parameter                                | 11 |

|   | 2.3 | Widel  | pand Radar/Satellite Receiver design Perspective                   | 13 |

|   |     | 2.3.1  | On Chip Blocker Removal Techniques for Wide Band Receiver          | 14 |

|   |     |        | 2.3.1.1 Feedforward                                                | 15 |

|   |     |        | 2.3.1.2 Feedback Interference Cancellation                         | 15 |

|   | 2.4 | Propo  | sed Design Concern on Wireless Receiver Approach                   | 18 |

|   |     | 2.4.1  | Identified Blockers and Strength                                   | 18 |

|   |     | 2.4.2  | Proposed Design Approach                                           | 18 |

|   | 2.5 | Summ   | nary                                                               | 19 |

| 3 | Hig | h Perf | formance Low Noise Main Path Receiver                              | 21 |

|   | 3.1 | Introd | luction                                                            | 21 |

|   | 3.2 | Wide   | Band Receiver Design Specification                                 | 22 |

|   |     | 3.2.1  | Sensitivity                                                        | 22 |

|   |     | 3.2.2  | Noise Figure                                                       | 23 |

|   |     | 3.2.3  | Selectivity                                                        | 23 |

|   |     | 3.2.4  | Linearity                                                          | 23 |

|   | 3.3 | Receiv | ver Front-End Architecture                                         | 24 |

|   |     | 3.3.1  | Target Specification                                               | 24 |

|   | 3.4 | Circui | t Implementations                                                  | 25 |

|     | 3.4.1 | Wide Band Low Noise Amplifier (LNA)                                | 5 |

|-----|-------|--------------------------------------------------------------------|---|

|     |       | 3.4.1.1 Composite Transistor Pair Bandwidth Enhanced Low noise am- |   |

|     |       | plifier (LNA)                                                      | 6 |

|     |       | 3.4.1.1.1 Input Matching Analysis                                  | 6 |

|     |       | 3.4.1.1.2 Noise Analysis                                           | 9 |

|     |       | 3.4.1.1.3 Gain Analysis                                            | 3 |

|     | 3.4.2 | Down Conversion Mixer                                              | 5 |

|     |       | 3.4.2.1 Transconductance Amplifier                                 | 6 |

|     |       | 3.4.2.2 Switches                                                   | 9 |

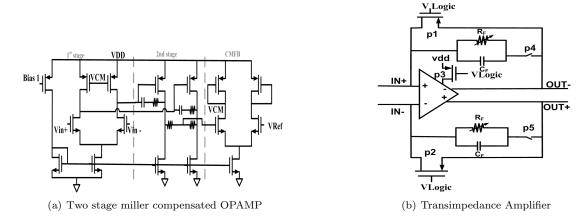

|     |       | 3.4.2.3 Transimpedance Amplifier                                   | 0 |

|     | 3.4.3 | Analysis of Down Conversion Mixer                                  | 2 |

|     |       | 3.4.3.1 Conversion gain of passive mixer                           | 2 |

|     |       | 3.4.3.2 Noise sources in passive mixer architecture                | 2 |

|     |       | 3.4.3.3 Linearity                                                  | 4 |

| 3.5 | Wide  | Band Receiver Taped Out Design                                     | 5 |

|     | 3.5.1 | Experimental Results                                               | 9 |

|     |       | 3.5.1.1 Measurement Results of LNA                                 | 9 |

|     |       | 3.5.1.1.1 Measurement setup                                        | 9 |

|     |       | 3.5.1.1.2 Result and Discussion                                    | 1 |

|     |       | 3.5.1.2 Measurement Results of Receiver                            | 5 |

|     |       | 3.5.1.2.1 Measurement setup                                        | 5 |

|     |       | 3.5.1.2.2 Result and discussion                                    |   |

| 3.6 | Summ  | ary                                                                |   |

| 5.0 | ~ amm | ···                                                                | - |

| 4 | Aux | kiliary | Path Ultra Low Power Out of Band Sensing Subthreshold Receiver 6 | 60 |

|---|-----|---------|------------------------------------------------------------------|----|

|   | 4.1 | Introd  | uction                                                           | 60 |

|   |     | 4.1.1   | Subthreshold MOS Operation                                       | 61 |

|   |     | 4.1.2   | Power Consumption in Wireless Front-ends                         | 65 |

|   | 4.2 | Subth   | reshold Low Noise Amplifier                                      | 65 |

|   |     | 4.2.1   | Design and Implementation Subthreshold LNA                       | 66 |

|   |     |         | 4.2.1.1 Wideband Input Matching, Gain and Noise Analysis:        | 66 |

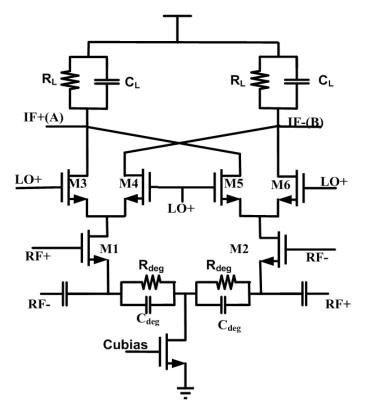

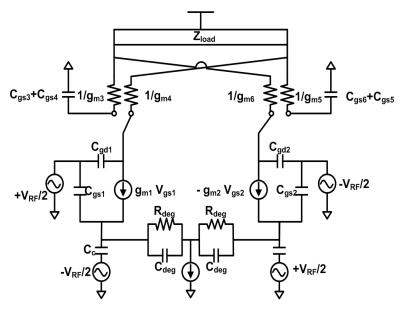

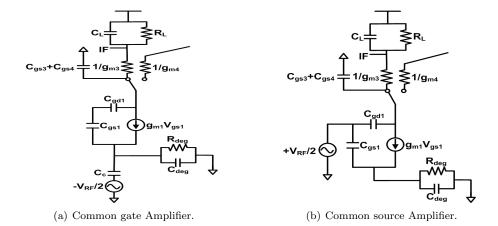

|   | 4.3 | Active  | e Gilbert Cell Down Conversion mixer                             | 67 |

|   |     | 4.3.1   | Transfer Function of Active Gilbert Cell Down Conversion Mixer   | 70 |

|   |     | 4.3.2   | Noise in Current-Commutating Mixers                              | 71 |

|   |     | 4.3.3   | Non-idealities of the Mixer                                      | 72 |

|   |     |         | 4.3.3.1 Intermodulation Distortion                               | 73 |

|   |     |         | 4.3.3.2 Integration issues                                       | 73 |

|   | 4.4 | Fabric  | ated Fully Subthreshold Receiver                                 | 74 |

|   |     | 4.4.1   | Measurement Results of Auxiliary Receiver                        | 77 |

|   | 4.5 | Perfor  | mance Summary                                                    | 81 |

|   | 4.6 | Summ    | ary                                                              | 82 |

| 5 | Rec | onfigu  | rable Mixers for RF Front End                                    | 83 |

|   | 5.1 | Introd  | $\operatorname{uction} \ldots \ldots \ldots \ldots \ldots$       | 83 |

|   | 5.2 | Wide-   | Band Reconfigurable (Active / Passive) Down Conversion Mixer     | 84 |

|   |     | 5.2.1   | Transconductance Amplifier                                       | 85 |

|   |     | 5.2.2   |                                                                  | 86 |

|   |     | 5.2.3   |                                                                  | 90 |

|   |     |         |                                                                  | 91 |

|   |     |         |                                                                  |    |

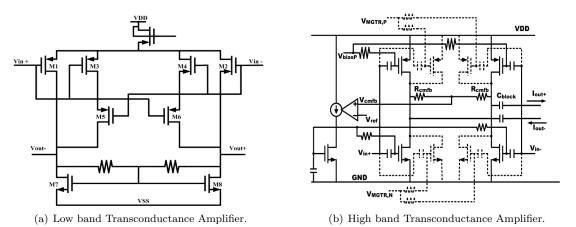

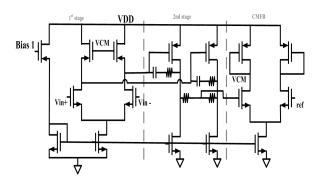

|                           | 5.3   | A Low  | V/High Band Parallel path TCA with configurable (Active / Passive) Down |     |

|---------------------------|-------|--------|-------------------------------------------------------------------------|-----|

|                           |       | Conve  | ersion Mixer                                                            | 93  |

|                           |       | 5.3.1  | Transconductance Amplifier                                              | 94  |

|                           |       | 5.3.2  | Active/Passive Mixer                                                    | 95  |

|                           |       | 5.3.3  | Transimpedance Amplifier                                                | 95  |

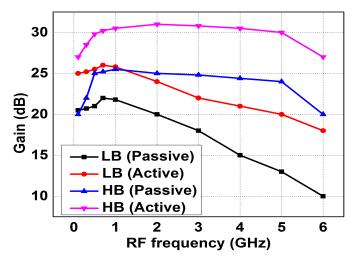

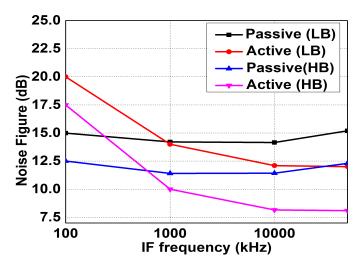

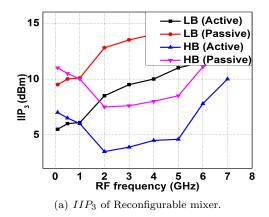

|                           |       | 5.3.4  | Simulated Result                                                        | 95  |

|                           | 5.4   | Recon  | figurable High/Low band Passive Down Conversion mixer for wide band     |     |

|                           |       | Receiv | <i>r</i> er                                                             | 98  |

|                           |       | 5.4.1  | Transconductance Amplifier                                              | 98  |

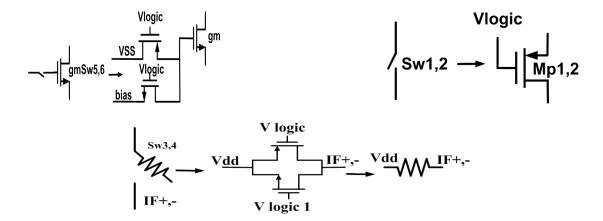

|                           |       | 5.4.2  | Switches                                                                | 100 |

|                           |       | 5.4.3  | Transimpedance Amplifier                                                | 101 |

|                           |       | 5.4.4  | Simulation Results                                                      | 102 |

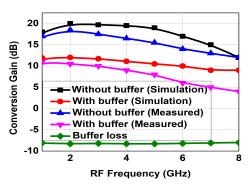

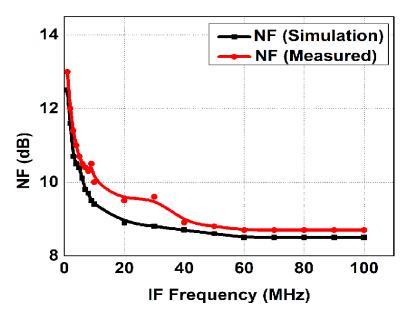

|                           | 5.5   | Fabric | eation of Wide-Band Reconfigurable (Active / Passive) Mixer             | 104 |

|                           |       | 5.5.1  | Measurement Result                                                      | 107 |

|                           | 5.6   | Summ   | nary                                                                    | 109 |

| 6                         | Cor   | clusio | n and Future Scope                                                      | 110 |

|                           | 6.1   | Concl  | usion                                                                   | 110 |

|                           | 6.2   | Future | e Scope                                                                 | 111 |

| $\mathbf{R}_{\mathbf{c}}$ | efere | nces   |                                                                         | 112 |

# List of Figures

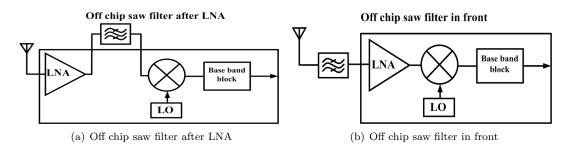

| 2.1  | Saw filter based receiver                                                    | 9  |

|------|------------------------------------------------------------------------------|----|

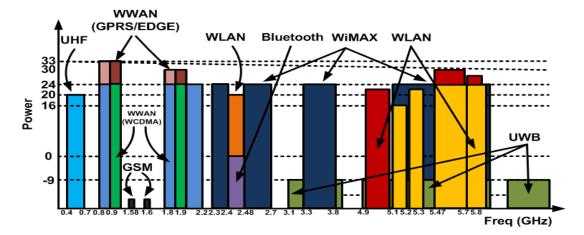

| 2.2  | Crowded radio spectrum with multiple standards                               | 10 |

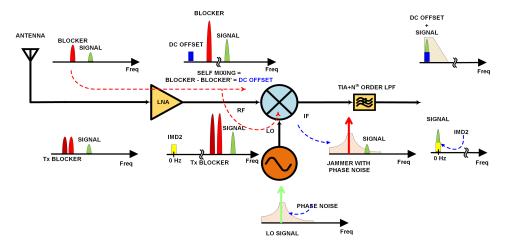

| 2.3  | Effects due to blocker and transmitter leakage blocker on wideband receivers | 11 |

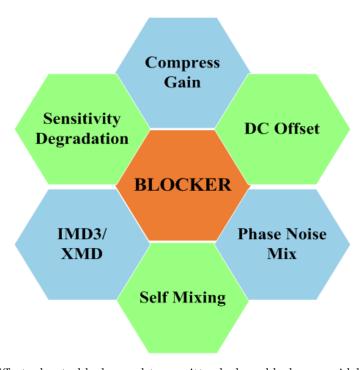

| 2.4  | Issues due to blocker on wideband receivers                                  | 12 |

| 2.5  | Gain Compression due to blocker                                              | 12 |

| 2.6  | Multi-band receiver each path saw in front                                   | 14 |

| 2.7  | Wide band receiver with configurable saw in front                            | 14 |

| 2.8  | Blocker removal techniques                                                   | 15 |

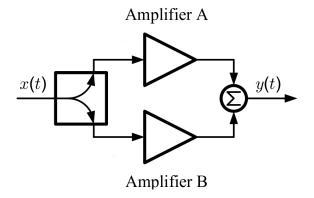

| 2.9  | Feedforward linearization technique                                          | 16 |

| 2.10 | Block diagram of feedback cancellation mechanism                             | 16 |

| 2.11 | Identified out of band blocker                                               | 18 |

| 2.12 | High Performance CMOS Wide-Band RF Front-End With Subthrehold Out of         |    |

|      | Band Sensing                                                                 | 19 |

| 3.1  | Front end Block Diagram                                                      | 24 |

| 3.2  | Proposed struture of LNA                                                     | 26 |

| 3.3  | Equivalent small signal model of LNA                                         | 27 |

| 3.4  | Simulated $S_{11}$ and $Z_{in}$ of proposed LNA                              | 28 |

| 3.5  | Noise equivalent of Low Noise Amplifier                                      | 29 |

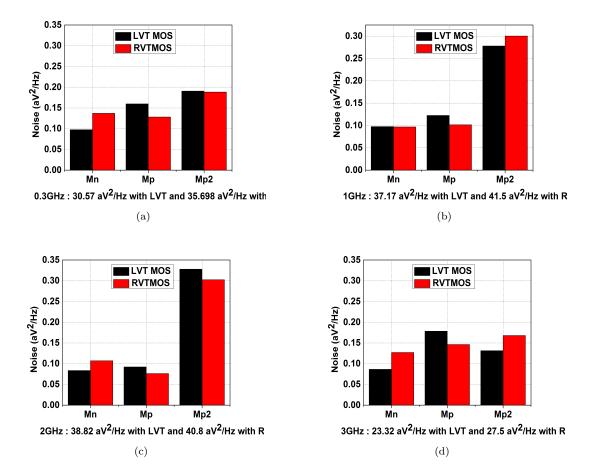

| 3.6  | Simulated Noise Figure with LVT MOS and RVT MOS of LNA                                | 32 |

|------|---------------------------------------------------------------------------------------|----|

| 3.7  | Noise contribution of individual MOS of LNA at different frequency $\dots$            | 33 |

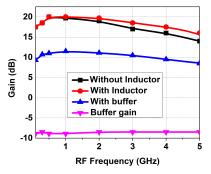

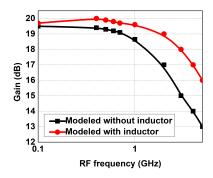

| 3.8  | Simulated and modeled conversion gain of LNA                                          | 34 |

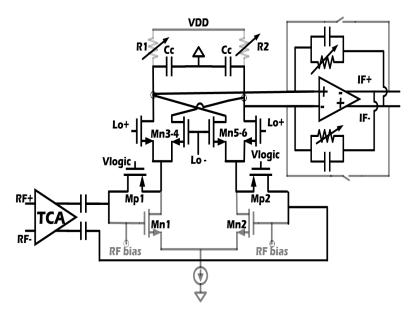

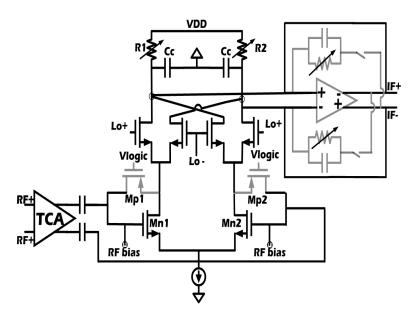

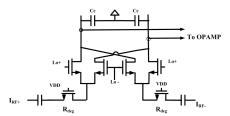

| 3.9  | Down Conversion Mixer conceptual diagram                                              | 35 |

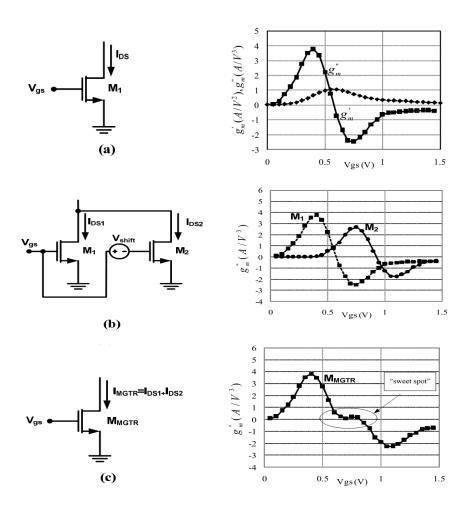

| 3.10 | Multigate Transistor Concept                                                          | 38 |

| 3.11 | Transconductance amplifier of down conversion mixer                                   | 39 |

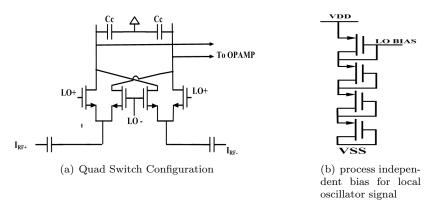

| 3.12 | Switching stage and its bias generation                                               | 40 |

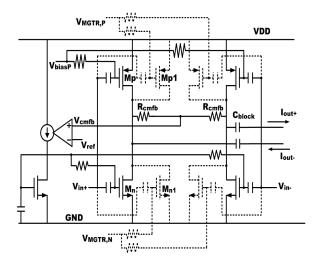

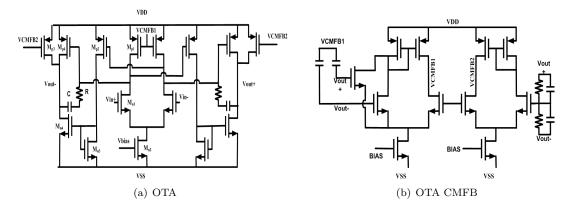

| 3.13 | Two stage OTA used for TIA                                                            | 41 |

| 3.14 | Circuit schematic of buffer used for output matching and measurement purpose          |    |

|      | of LNA                                                                                | 45 |

| 3.15 | Schematic diagram of bias generation core                                             | 47 |

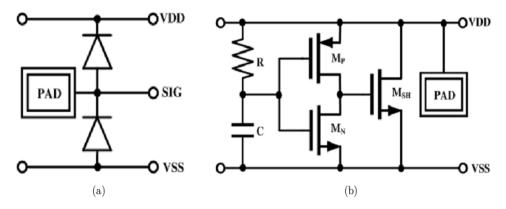

| 3.16 | Pad structure with ESD diode protection                                               | 48 |

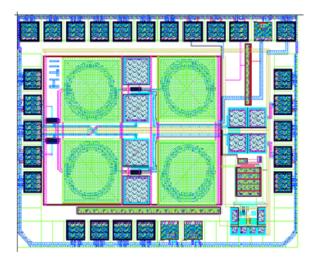

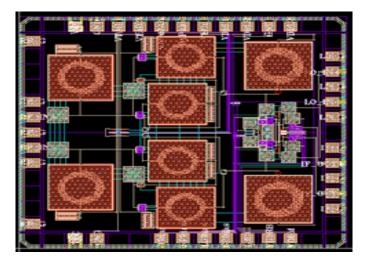

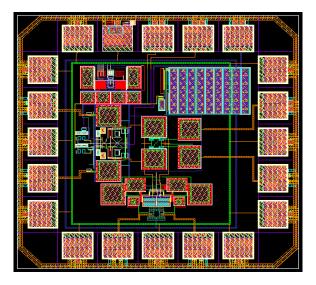

| 3.17 | LNA layout                                                                            | 49 |

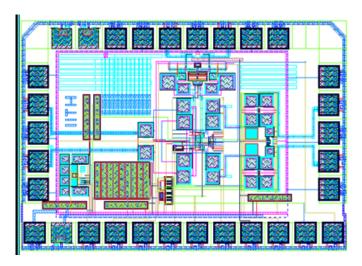

| 3.18 | Post layout of main path Receiver                                                     | 49 |

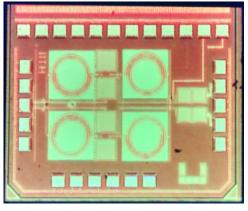

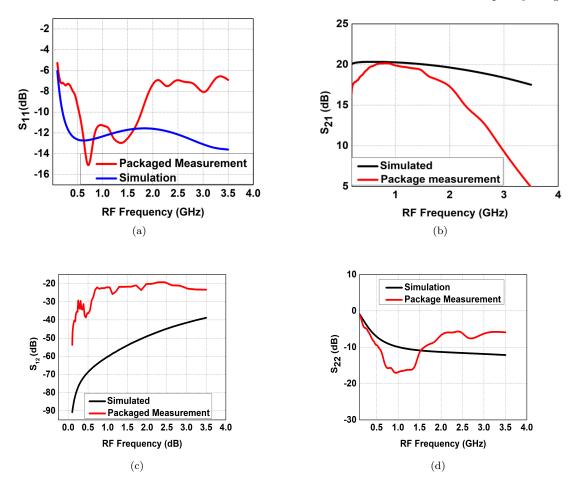

| 3.19 | Chip microphotograph and assembled board of LNA $\ \ldots \ \ldots \ \ldots \ \ldots$ | 50 |

| 3.20 | Measurement set of Noise Figure                                                       | 50 |

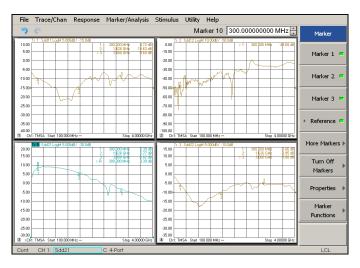

| 3.21 | Measured S parameter of LNA with buffer from Network Analyzer                         | 51 |

| 3.22 | Measured S parameter of LNA without buffer                                            | 52 |

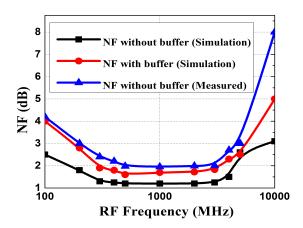

| 3.23 | Measured Noise figure of LNA                                                          | 53 |

| 3.24 | Measured 1dB-CP at 1.2GHz of LNA                                                      | 54 |

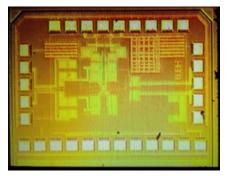

| 3.25 | Microphotograph of main Receiver                                                      | 55 |

| 3.26 | Test board and chip on board receiver                                                 | 56 |

| 3.27 | Measured input reflection of main Receiver                                            | 56 |

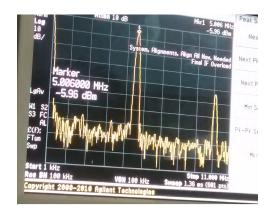

| 3.28 | Spectrum of main receiver @ -31dBm RF input power                                     | 57 |

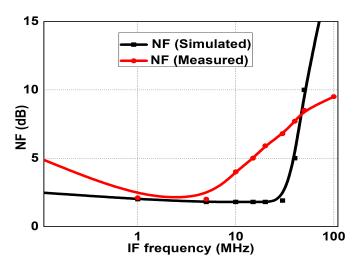

| 3.29 | Measured noise figure of receiver                                                     | 57 |

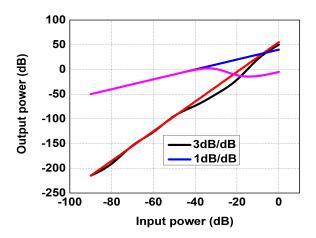

| 3.30 | $IIP_3$ of main receiver                                                             | 58 |

|------|--------------------------------------------------------------------------------------|----|

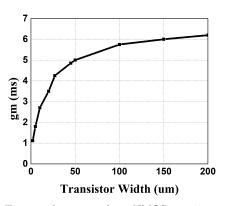

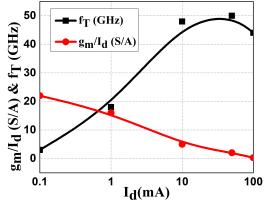

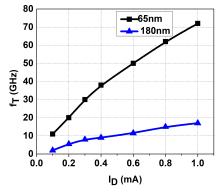

| 4.1  | Transconductance and $f_T$ plot of NMOS transistor                                   | 62 |

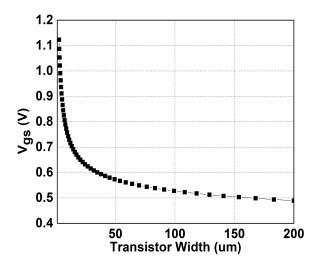

| 4.2  | Width vs $V_{gs}$ NMOS transistor with 0.18 $\mu m$ length (L) and a bias current of |    |

|      | $300\mu$ A                                                                           | 63 |

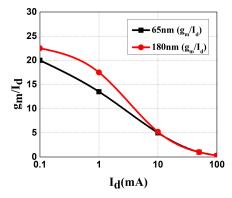

| 4.3  | gm/ID and $f_T$ plot of subthrehold MOS                                              | 64 |

| 4.4  | Low Noise Amplifier for subthreshold receiver                                        | 66 |

| 4.5  | Proposed Gilbert Cell (Active Gilbert cell Down conversion Mixer with bandwidth      |    |

|      | Extension) for subthreshold receiver                                                 | 68 |

| 4.6  | Small signal model of proposed gilbert cell                                          | 68 |

| 4.7  | Superposition theorem in CCC in input pair of mixer                                  | 69 |

| 4.8  | Bandwidth extension using capacitive degeneration                                    | 71 |

| 4.9  | Noise sources in Proposed Down Conversion Mixer                                      | 72 |

| 4.10 | Block diagram of Subthreshold receiver                                               | 74 |

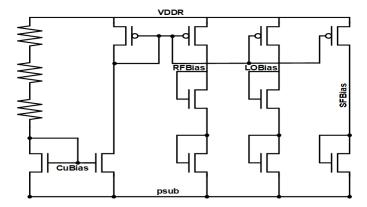

| 4.11 | Schematic diagram of bias generation circuit                                         | 76 |

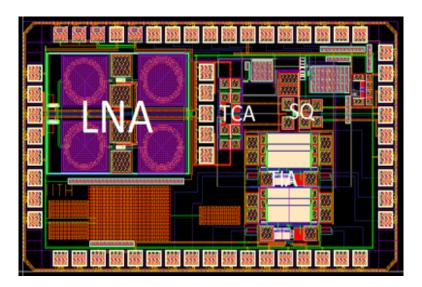

| 4.12 | Complete layout diagram of subthreshold receiver                                     | 76 |

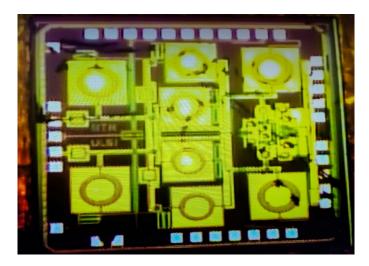

| 4.13 | Die photograph of Subthreshold receiver                                              | 77 |

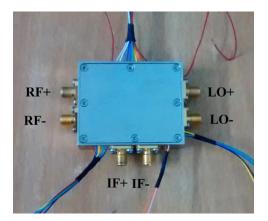

| 4.14 | Assembled test board and module                                                      | 78 |

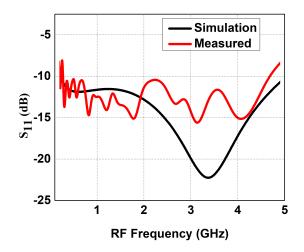

| 4.15 | S11 of Subthreshold (Auxiliary) Receiver                                             | 79 |

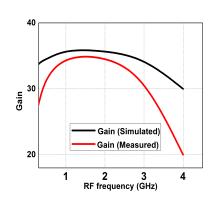

| 4.16 | Measured Conversion gain of subthreshold receiver @ 50<br>MHz IF frequency           | 79 |

| 4.17 | Measured noise figure of subthreshold receiver                                       | 80 |

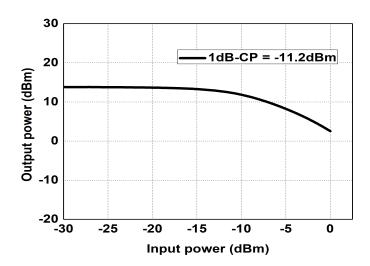

| 4.18 | Measured 1dB-CP of subthreshold receiver                                             | 80 |

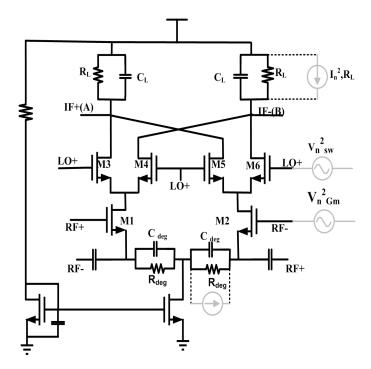

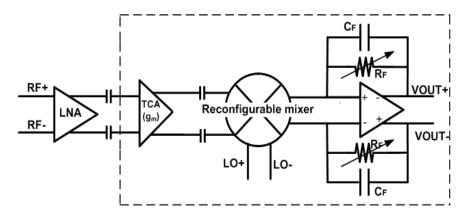

| 5.1  | Wide-band reconfigurable down conversion mixer                                       | 84 |

| 5.2  | Transconductance Amplifier                                                           | 85 |

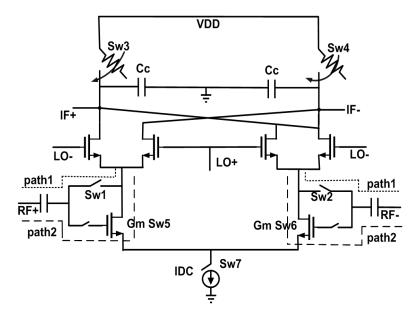

| 5.3  | Reconfigurable down conversion mixer                                                 | 87 |

| 5.4  | Passive mode                                                              | 88  |

|------|---------------------------------------------------------------------------|-----|

| 5.5  | Active mode                                                               | 88  |

| 5.6  | Switch Implementation                                                     | 89  |

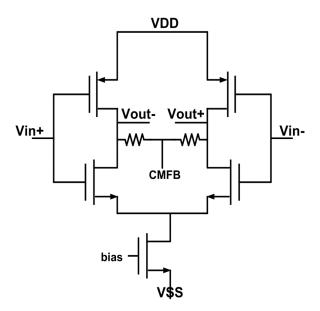

| 5.7  | Transimpedamce Amplifier                                                  | 90  |

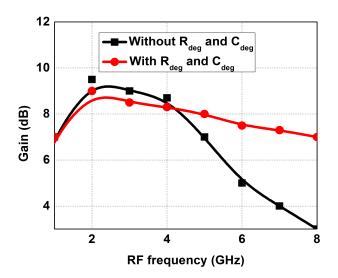

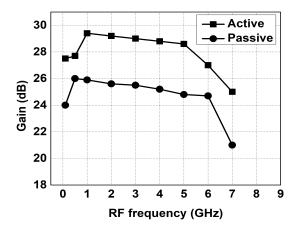

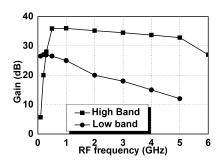

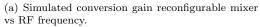

| 5.8  | Simulated conversion gain reconfigurable mixer vs RF frequency            | 91  |

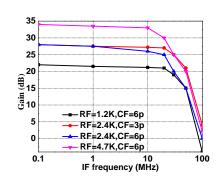

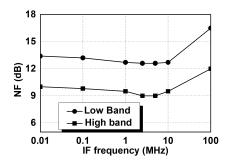

| 5.9  | Simulated noise figure and conversion gain vs IF frequency                | 92  |

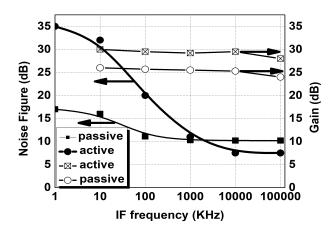

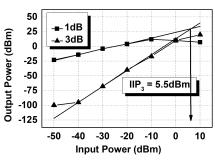

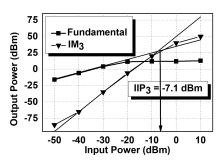

| 5.10 | Simulated linearity of reconfigurable mixer                               | 92  |

| 5.11 | Low/High Band Parallel path TCA with configurable (Active / Passive) Down |     |

|      | Conversion Mixer                                                          | 94  |

| 5.12 | Low / High band Transconductance Amplifier                                | 95  |

| 5.13 | Simulated conversion gain reconfigurable mixer vs RF frequency            | 96  |

| 5.14 | Simulated noise figure vs IF frequency                                    | 96  |

| 5.15 | Simulated linearity and Gain of reconfigurable mixer                      | 97  |

| 5.16 | Reconfigurable High/Low band Passive Down Conversion mixer                | 98  |

| 5.17 | Reconfigurable High/Low band Transconductance Amplifier                   | 100 |

| 5.18 | Low / High Band reconfigurable Transconductance Amplifier                 | 100 |

| 5.19 | Switching Quad with degeneration resistance                               | 101 |

| 5.20 | Two stage miller compensated OPAMP                                        | 101 |

| 5.21 | Layout of Reconfigurable Down Conversion Mixer                            | 102 |

| 5.22 | Simulated conversion gain and noise figure of reconfigurable mixer        | 103 |

| 5.23 | Simulated linearity of reconfigurable mixer                               | 103 |

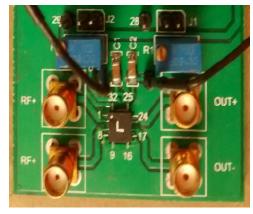

| 5.24 | GDSII of reconfigurable down conversion mixer                             | 106 |

| 5.25 | Die photo and assembled board of Reconfigurable Mixer                     | 107 |

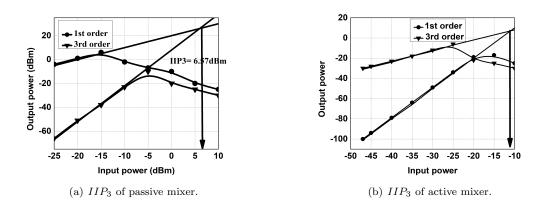

| 5.26 | Conversion gain of reconfigurable down conversion mixer                   | 108 |

| 5.27 | Noise Figure of reconfigurable down conversion mixer                      | 108 |

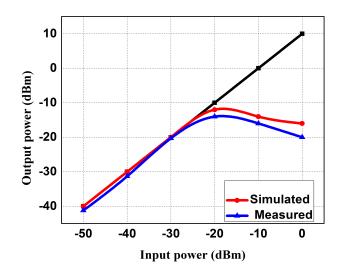

| 5.28 Measured linearity of Reconfigurable down conversion Mixer | 108 |

|-----------------------------------------------------------------|-----|

|-----------------------------------------------------------------|-----|

### List of Tables

| 2.1  | Blocker effect on receiver                                                        | 13 |

|------|-----------------------------------------------------------------------------------|----|

| 2.2  | Receiver specification for radar and satellite Application                        | 17 |

| 3.1  | Review of recent wideband receiver                                                | 22 |

| 3.2  | Full system specification of main path receiver                                   | 24 |

| 3.3  | Review of recent wideband LNA                                                     | 25 |

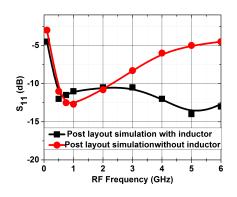

| 3.4  | Input reflection with and without inductor                                        | 28 |

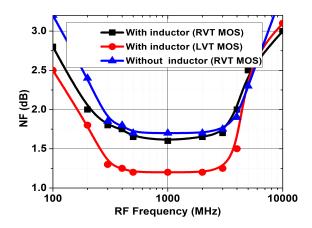

| 3.5  | Simulated Noise figure summary with RVT CMOS and LVT CMOS of LNA                  | 32 |

| 3.6  | Review of recent down conversion mixer                                            | 35 |

| 3.7  | Circuit element values and transistor aspect ratio for the implemented LNA and    |    |

|      | Buffer                                                                            | 46 |

| 3.8  | Circuit element values and transistor aspect ratio of TCA                         | 46 |

| 3.9  | Circuit element values and transistor aspect ratio of OTA                         | 47 |

| 3.10 | Measured Results and comparision of LNA                                           | 54 |

| 3.11 | Measured results and Comparison of main path Receiver                             | 59 |

| 11   | Review of recent ultra low power wideband receiver                                | 61 |

| 4.1  |                                                                                   | 01 |

| 4.2  | Circuit element values and transistor aspect ratio for the implemented subthresh- |    |

|      | old LNA                                                                           | 75 |

| 4.3 | Circuit element values and transistor aspect ratio for the implemented subthresh- |     |

|-----|-----------------------------------------------------------------------------------|-----|

|     | old Mixer                                                                         | 75  |

| 4.4 | Performance summary with comparison of subthreshold receiver                      | 81  |

| 5.1 | Review of recent reconfigurable wideband LNA and mixer                            | 84  |

| 5.2 | Simulation results of Reconfigurable mixer and Comparison                         | 93  |

| 5.3 | Simulation results of Low/High Band Parallel path TCA with configurable (Active   |     |

|     | / Passive) Down Conversion Mixer and Comparison                                   | 97  |

| 5.4 | Simulation results of Reconfigurable High/Low band Passive Down Conversion        |     |

|     | mixer for wide band Receiver and Comparison                                       | 104 |

| 5.5 | Circuit element values and transistor aspect ratio for the tapeout Reconfigurable |     |

|     | (Active/Passive) Mixer                                                            | 105 |

| 5.6 | Performance summary of measured results                                           | 109 |

### Chapter 1

### Introduction

### 1.1 Introduction

Wireless communications have proliferated and penetrated into daily life as a result of decades of continuous advancements in communications and semiconductor technologies. With the introduction of new applications, services and the increasing demand for higher data rate comes the need for new frequency bands and new standards. A wide variety of applications, ranging from Global Positioning System (GPS), cellular communications, Wi-Fi Local Area Network, and short-range personal communications such as Bluetooth (BT), have been commercially deployed and continue to evolve. On the emerging horizon, mobile terminals no longer limit their usage to a single purpose, but serve to provide a multitude of access to heterogeneous networks over which rich service contents are delivered by concurrent or switchable operation of/among different link communications.

One critical issue for next generation wireless receiver for radar and military application is how to support multibands while not increasing the cost and power consumption. Multiple narrowband CMOS receiver front-ends with external RF filtering are well known approach in the past and the various efficient filter techniques were proposed to prevent large out-of-band signals corrupting the wanted signal. However, multiple RF front-end with filters make the system costly as well as bulky. So a feasible solution is the concept of the software-defined radio where

a single receiver can operate in different modes, each of which supports one or several bands and/or standards. To implement such a receiver, a wide band radio frequency (RF) building blocks, such as the Low Noise Amplifier (LNA), mixer etc., are required. Now, such multiband receiver LNA, picks up the strong in-band /out of band blockers signal from unintended uplink communications with the desired receiving signal. The amplitude of these blockers signals is usually much larger than the desired signal. If not appropriately corrected, they will affect the receiver response and block the healthy receiving of the intended signal. The impacts of blockers include desensitizing the receiver sensitivity, compressing amplifier gain and eventually driving circuits into saturation, increasing signal distortion and reciprocally mixing with LO phase noise, all of which deteriorates link performances such as receiver bit error rate.

Standalone radio mitigates the blocker issue by placing high-Q filters in front of the LNA to reject the unwanted signal energy. However, existing solutions rely on MEMS technology and needs to solve practical issues such as minimizing the extra fabrication cost and improving the yield. For at least three reasons, active filters have made little impact in super heterodyne receivers, where a bandpass filter with poles selects the desired channel at some intermediate frequency (IF). First, the power dissipation of an active bandpass filter rises proportionally to the center frequency and the required dynamic range. Second, it is increasingly difficult because of parasitic effects to accurately realize high poles at high center frequencies. Third, it is difficult to meet the specifications on distortion because the filter must handle signals and interferers which are amplified by the frontend. For these reasons, ceramic and surface acoustic wave (SAW) filters tuned to frequencies from 100's of kHz to 100's of MHz are used in vast numbers in production broadcast radio receivers and conventional cellular telephone handsets, but saw filter makes receiver narrowband. So for continuous wide band receiver a tunable RF filter suits better for dynamically reconfigurable blocker rejection. Our aim is to design low noise, wide band receiver for radar and satellite application with out of band blocker sensing and rejection at the input stage.

### 1.2 Aim and Motivation

(Complementary Metal Oxide Semiconductor) CMOS technologies with aggressive scaling improves area and power consumption with high enough  $f_T$  to accommodate most existing commerical applications under 10GHz. Compatibility with the digital part of the transceiver mandates the use of advanced (scaled down) CMOS process. With its ability of highest level of integration, low cost, and low power consumption, CMOS is a MUST for SOCs consumer electronic products.

Different communication standards exist currently where most of them are allocated in the spectrum from 400MHz to 6GHz. Traditionally, each standard requires separate RF front-end and digital resources for baseband processing. Presently, the existing designs are in form of single band specific L/S/C and the number of used chips also limited. This has given rise to a need for receivers that are compatible with as many standards and frequency bands as possible. Now a day, researcher in academic/industry is looking to integrate all L / S /C bands in the form of a single receiver in CMOS. So above approach is power hungry, costly and take more area. To exemplify this point, a multiband Radar/Satellite Receiver front-end can be designed

The noisy radio frequency (RF) environment demands a very stringent blocking requirement for most wireless applications. To address both inband/outband interference issues in broadband single receiver front-end (BSRFE), various blocker cancellation techniques are used to improve the dynamic range of receivers as (a) Notch filter [1]- [2], (b) SAW filter [3]- [4], (c) SAW less [5]- [6], (d) Coupled inductor in LNA [7], (e) N path filter [8], (f) Self-Interference Cancellation [9], (g) An Active Feedback Interference Cancellation Technique [10], (h) A Feedforward approach [11], (i) A Digital cancellation, etc. In digital cancellation, along with main receiver, an additional reference receiver is employed for capturing these blockers [12]. So, receiver must satisfy a certain blocking template defined at various blocker frequencies and levels. Here mostly out of band blockers have been considered.

Hence, in this dissertation, an out of band blocker sensing multipath scheme is depicted with a major focus in the design, analysis and realization of a high performance wideband receiver architecture. A subthreshold (ultra low power) receiver is designed for out of band sensing. In main path receiver, a high gain differential LNA with bandwidth enhanced noise figure

minimization technique and a passive mixer with linearity improved integrated baseband filter are proposed and verified in CMOS process. Further, a standalone re-configurable active/passive mixer stage is proposed and a comparison is drawn with previous passive one in simulation mode

### 1.3 Highlights of Research Investigations

- Comprehensive review of blocker rejection wireless receiver techniques for high performance receiver.

- Wide band and noise optimized LNA design techniques has been proposed.

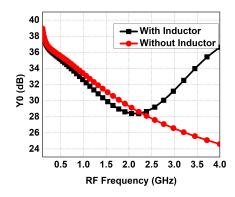

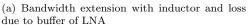

- Detailed Analysis of impact of inductor on input matching, gain bandwidth and noise figure of LNA.

- Noise optimization by using LVT MOS and how it does'nt impact on input matching of LNA.

- High performance low noise, bandwidth extensive Main path receiver has been designed, simulated and fabricated in 65nm CMOS and verified by measurements.

- Subthreshold receiver or auxiliary path receiver for out of band sensing and rejection to achieve better linearity.

- Subthreshold LNA and active mixer is optimized for ultra low power and wide band.

- Reconfigurable Mixer in the form of Active/Passive, RF bandwidth, noise and power

#### 1.4 Overview of Thesis Contribution

#### 1.4.1 Blocker Rejection Wireless Receiver Techniques

A comprehensive review of out of band blocker rejection is presented. Blocker effects on various performance parameter like gain compression, DC offset, phase noise mixing, self mixing, sensitivity, IMD3/XMD of receiver, how it is impacting on various parameter of wireless front-end

receiver. Further Various blocker rejection techniques (onchip/offchip) of wideband receiver has been discussed to reject out of band blockers. Pros and cons of each technique is presented in brief. Further a brief introduction of wideband Radar/Satellite Receiver design challenges, proposed design concern on wireless receiver approach, identified blocker and their strength for desired bandwidth has been illustrated. A new approach is presented to reject out of band blocker by using a multipath scheme or auxiliary path receiver without effecting the performance of main path receiver.

### 1.4.2 High Performance Bandwidth Extension Low Noise Main Path Receiver

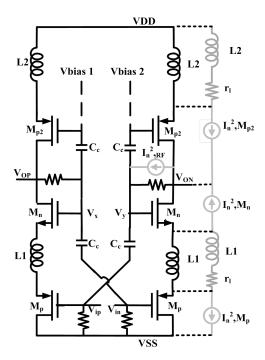

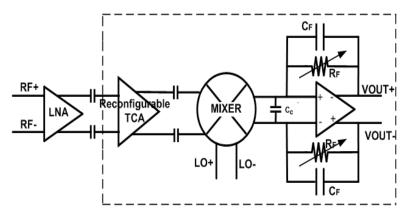

A wideband with low Noise RF front end receiver is extensively demanding in market for various application. The proposed receiver employs LNA, MGTR TCA, switching quad, biquad filtering. Wideband low noise amplifier is considered first main building block of receiver followed by mixer (active/passive). Wide band receiver performance parameter like input matching, noise, gain are mainly limited by LNA. The impedance matching of LNA is considered to be more essential for wide band design to achieve wide band gain and noise flatness in lower technology node designs. In general, passive components (in particularly inductors) realized in present day CMOS technologies, exhibit considerable resistive losses (finite Q-factor) are used to enhance bandwidth. To achieve below 1.7dB noise figure is still challenging in CMOS technology and in this context NMOS/PMOS cross coupled transistor pair LNA technique is chosen to improve performance like gain BW and noise figure. This approach also cancel the noise generated by input transistor, hence lowers the noise figure. Degenerative inductor is introduced at the source of mosfet to achieve wide band input matching and gain flatness at higher frequencies. Further provide better headroom voltage headroom in cascode topology RVTMOS is replaced by LVTMOS. After replacing RVTMOS with LVTMOS to provide equivalent gm (maintaining gain and input matching) aspect ratio of LVTMOS is reduced. Thus it is concluded that thermal noise will decrease by using LVTMOS as width of the MOS decreases. By decreasing width with maintaining same gm achieved noise figure of LNA with LVT MOS is 1.2dB. Thus resistive feedback LNA noise can be further reduced by using LVTMOS. Further a passive mixer (including

TCA, switches and TIA ) is incorporated. Linearity cancellation technique (MGTR TCA) is incorporated in TCA to achieve high linearity. Tow Thomas biquad filtering is applied to relax the linearity requirement of the following stage. Further all blocks are integrated in 65nm CMOS technology, taped out, fabricated. This concept is validated through a circuit simulations and real time measurements.

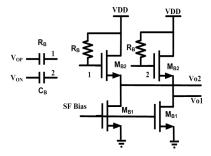

# 1.4.3 Auxiliary Path Ultra low power Out of Band Sensing Subthreshold Receiver

In recent days, the subthreshold bias technique is being preferred for realizing ultra low power receivers by exploiting the advantage of high  $g_m/I_D$  in this region. However, circuits designed in subthreshold region face design ambiguity due to the rise in parasitic capacitances and reduction of transit frequency  $(f_T)$ . To overcome these issues, appropriate circuit techniques using passive components need to be incorporated. To design, wide band receiver with ultra low power is a major challenge. In this receiver, a fully integrated receiver frontend which is composed of a low-noise amplifier and a down conversion mixer is designed for multiband applications. The DC power reduction is achieved by driving the MOS in subthreshold region. However, achieving good input matching in presence of larger devices is a challenging task. Moreover, the increased thermal noise of MOS transistors in weak inversion region imposes the need of noise cancellation circuitry which increases the power consumption. Hence, conventional topologies such as common gate, resistive feedback, distributed amplifier and Complementary MOS circuit cannot be applied as it is, for realizing a low power wideband LNA in subthreshold LNA. To implement a low power ultra wideband LNA in subthreshold region, the conventional common gate topology is modified to provide wideband input matching and a current reuse noise cancelling technique is introduced to improve noise performance. Further to implement a low power ultra wideband down conversion mixer in subthreshold region, the conventional gilbert cell topology is modified. A RC degeneration is used to formulated wide band mixer. By introducing capacitive degeneration a zero has introduced in transfer function to increase gain bandwidth. and resistive degeration is compensated by cross coupling the input RF signal. A wideband RF front end receiver operating from 2G - 5GHz is designed in a 180nm RFCMOS technology, for out

of band blocker sensing. This concept is validated through circuit simulations and real time measurements.

#### 1.4.4 Reconfigurable Down Conversion Mixer

To get a cost effective solution, a re-configurable single radio (that can configure to multi-mode as need basis) would be the best choice. To make the radio reconfigurable researchers introduce the RF transceiver front-end with reconfigurable LNA, PA, PLL, mixer, and filter etc. Among them, our emphasis is to design a Mixer that can provide reconfigurability on the performances like gain, linearity, noise figure and RF and IF bandwidth selection. Most of proposed reconfigurable mixer have shown gain variability and bandwidth tuning through current variation, load tuning etc.

# 1.4.4.1 Reconfigurable Active/Passive Down conversion mixer for wideband Receiver

Wideband (WB) reconfigurable down-conversion mixer for multi-standard wireless receivers is designed. The proposed mixer is re-configurable between active mixer and passive mixer modes. Reconfigurability is made through switching the input signal between gate and source terminal of input transistors and enabling/disabling the transimpedance stage at the output. The CMOS transmission gate (TG) switches are designed to provide optimum headroom in this low voltage design. The proposed circuit is designed in UMC 65nm RFCMOS technology with 1.2V supply voltage. This concept is validated through circuit simulations and real time measurements. Hence this circuit will be much helpful in multi-standard receiver design in IoT perspective.

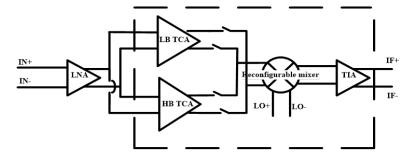

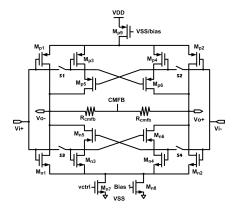

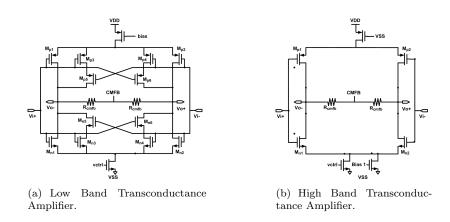

# 1.4.4.2 A Low/High Band Parallel path TCA with configurable (Active/Passive) Down Conversion Mixer

Down conversion mixer described in avove section has configurability between active and passive modes with gain and noise tunability but there is no configurability in RF bandwidth. To Reconfigure RF bandwidth, a down conversion mixer for a multistandard wireless receiver, with

adapted reconfigurability in the form of RF bandwidth, active/passive and IF bandwidth is proposed. In the proposed architecture RF bandwidth reconfigurability is reconfigured between low band (LB) RF frequency and high band (HB) RF frequency mixer modes. LB/HB reconfigurability is made through power switching the transconductance amplifier. Active/Passive reconfigurability is made through switching the input signal between gate and source terminal of input transistors and enabling/disabling the transimpedance stage at the output. The CMOS transmission gate (TG) switches are designed to provide optimum headroom in this low voltage design. The proposed circuit is designed in the UMC 65nm RFCMOS technology with 1.2V supply voltage

# 1.4.4.3 Reconfigurable High/Low band Passive Down Conversion mixer for wide band Receiver

In above section RF configurability is done by power switching HB/LB transconductance amplifier. Further to reduce the area of the chip down conversion mixer is designed with RF bandwidth reconfigurability in single circuitry by using switches. This reconfigurability is in the form of RF bandwidth, power consumption. In the proposed architecture RF bandwidth reconfigurability is reconfigured between low band(LB) RF frequency and high band (HB) RF frequency mixer modes. LB / HB reconfigurability is made through switching the transconductance amplifier between these two modes. So power can be saved while operating in desired mode. The proposed circuit is designed in UMC 65nm RFCMOS technology with 1.2V supply voltage. Full inductorless can operate over a wide frequency range.

### Chapter 2

### **Blocker Rejection Wireless**

## Receiver Techniques

### 2.1 Introduction

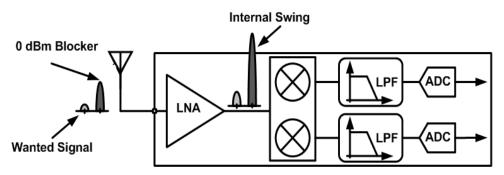

Any wireless receiver, receives signal transmitted by antenna, A wireless receiver front-end down shifts the frequency and demodulates the signal to retrieve the transmitted data. Receiver main blocks are LNA and mixer, shown in Fig. 2.1 which performs band selection, amplification and frequency down conversion. Whereas baseband section does channel selection, additional amplification (if required), demodulation and retrieval of data.

Figure 2.1: Saw filter based receiver.

The most important specifications of a RF receiver (saw or saw-less) is its sensitivity and

selectivity. Receiver sensitivity is the weakest signal level, it can detect with acceptable signal-to-noise ratio (SNR). Whereas selectivity is a measure of immunity to interferers and blockers close to its working frequency. These parameter can degrade the receiver performance such as noise figure and linearity. Saw filter based design are very famous for narrow band receiver as shown in Fig. 2.1(a) and Fig. 2.1(b) to remove out of band blocker (to achieve better linearity). In this chapter various metrics of blocker has been discussed in detail, and particularly their impact on receiver performance. Further various techniques have been explored to reject out of band blocker.

### 2.2 Effect of Blocker on Wideband Receiver

Most of the communication standards are allocated from 400MHz - 6GHz as shown in Fig. 2.2. Traditionally any receiver, receives all the band simultaneously from antenna, so there is a need to reject undesired band at the input of receiver otherwise receiver performance will reduce.

Figure 2.2: Crowded radio spectrum with multiple standards

The noisy radio frequency (RF) environment demands a very stringent blocking requirement for most multiband applications. Generally, the blocker may affect the receiver in two ways, 1) a large out-of-band blocker can saturate the receiver frontend, and hence by reducing the receiver gain, elevate the noise contribution of the following baseband blocks. 2) an in-band blocker may desensitize the receiver due to reciprocal or spurious mixing, or through inter-modulation. While the in-band blockers are typically removed by adjusting the local oscillator (LO) phase noise and linearity of the receive path, and ultimately through baseband filtering. The large out-of-band blockers may only be eliminated through front-end filtering otherwise it effects serious issues on receiver shown in Fig 2.3. Thus removing this type of interference is considered as a crucial issue in designing RF transceivers.

Figure 2.3: Effects due to blocker and transmitter leakage blocker on wideband receivers

#### 2.2.1 Blocker Impact on Various Parameter

Blocker and Tx leakage may affect the receiver by following ways shown in Fig. 2.4 in the form of [13]. The problem of gain compression is demonstrated in Fig. 2.5. A conventional wide band design has no selectivity and amplifies both the wanted signal and any blockers present Fig. 2.5. Given the voltage amplification required to achieve a competitive noise figure and the low supply voltages used in modern CMOS processes, a 0dBm blocker will cause the LNA to clip. This will increase noise and distortion in the receiver. Since the desired signal is weak, the low-noise amplifier (LNA) gain must be kept high.

Figure 2.4: Issues due to blocker on wideband receivers.

Figure 2.5: Gain Compression due to blocker

Similarly once blocker amplified by LNA, may find a path to the LO input port of the mixer, thus producing self mixing shown in Fig 2.4, which is a DC component at the mixer output and aggravates sensitivity as well. In addition, if the blocker has high phase noise, which also contributes to the overall noise floor level. If blocker has low phase noise and Rx LO has finite phase noise that mixes with blocker, and creates reciprocal mixing at the mixer output, degrades sensitivity also. If the blocker is near to receiver signal, blocker and transmitter leakage will cause  $3^{rd}$  order intermodulation (IMD3) and cross modulation(XMD) simultaneously due to LNA nonlinearity. Both IMD3 and XMD are near to receiver signal, resulting in sensitivity degradation. Besides, if the blocker is near to transmitter signal in spectrum, LNA nonlinearity also causes IMD2, which is like DC offset, and will aggravate sensitivity. Blocker affect has summarized in Table 2.1 and thus the blocker must be filtered prior to reaching the amplifier

|                   | With blocker | With blocker and Tx leakage |

|-------------------|--------------|-----------------------------|

| Gain Reduction    | yes          | yes                         |

| DC Offset         | yes          | yes                         |

| Self Mixing       | yes          | yes                         |

| Phase Noise       | yes          | yes                         |

| Reciprocal mixing | yes          | yes                         |

| IMD3              |              | yes                         |

| XMD               |              | yes                         |

| IMD2              |              | yes                         |

Table 2.1: Blocker effect on receiver.

output. On the other hand, due to the modest quality factor (Q) of on-chip inductors, it is not practical to integrate such a sharp filter on-chip. For these reasons, all the existing receivers inevitably use an external surface acoustic filter.

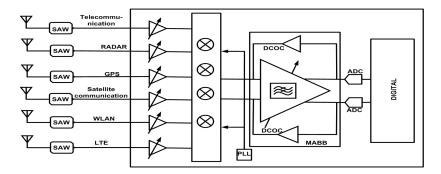

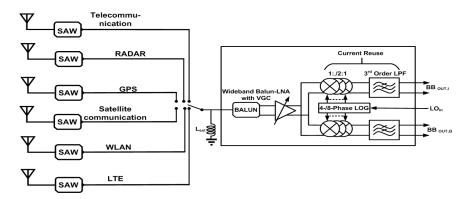

### 2.3 Wideband Radar/Satellite Receiver design Perspective

Today, L/S band (1-2GHz, 2-2.7GHz) radio are widely spread in various defense, military and satellite applications. Presently, the existing designs are form of single band specific to one of L/S band and the number of used chips also limited. Although CMOS technology is cost effective (mass scale perspective), less area and power consumption but they commercially accepts more than 6 numbers of wafer. So these radios is designed in costly III-V technology as these foundry commercially accepts single wafer solution. Now a day, researcher in academic/industry is looking to integrate all L [14] [15] [16] [17]/S [18] [19] [20] [21] [22]/C [23] [24] [25] bands in the form of a single receiver in CMOS and also how to implement a highly integrated RF front-end that can operate at low power consumption without compromising the performance. To exemplify this point, a multiband Radar/Satellite Receiver front-end can be designed in the form of in Fig. 2.6 [26] and Fig. 2.7 [27].

But there are several disadvantages of using saw filter in wide band receiver.

1. It increases the cost, especially in multimode and multiband applications where several of these filters are needed.

Figure 2.6: Multi-band receiver each path saw in front

Figure 2.7: Wide band receiver with configurable saw in front.

- 2. The insertion loss of the SAW filter, typically as high as 2–3 dB, directly degrades the receiver sensitivity.

- 3. It removes the flexibility of sharing the LNAs in multimode or multiband applications, and particularly in software-defined radios.

Therefore, it is highly desirable to eliminate external saw filters. But it is important to remove blocker at input otherwise it can degrade receiver performance, so on-chip blocker removal techniques like feed-forward and feed-backward approach need to be investigated into these designed.

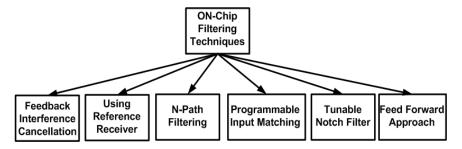

#### 2.3.1 On Chip Blocker Removal Techniques for Wide Band Receiver

The problem of interference removal has been studied extensively in the past in various contexts, including background noise reduction in acoustic systems. These techniques employ mainly

out of band rejection by having on-chip filtering. To address outband interference issues in

Figure 2.8: Blocker removal techniques

broadband single receiver front-end (BSRFE), various on-chip blocker cancellation techniques has been proposed, as shwon in Fig. 2.8 are used to improving the dynamic range of receivers as (a) Passive on-chip filtering [28],(b) Notch filter [1]- [2], (c) Coupled inductor in LNA [7], (d) N path filter [8], (e) Programmable filter [29], (f) Self-Interference Cancellation [9] (g) An Active Feedback Interference Cancellation Technique [10],(h) A Feedforward approach [11], (i) A Digital cancellation by using reference receiver etc. [12]. But passive filters are hard to tune, which makes design non tunable and narrow band, so feedforward and feedbackward design came into picture.

#### 2.3.1.1 Feedforward

One way of reducing the out-of band blocker is through feed-forward injection shown in Fig. 2.9, where a replica of the blocker is subtracted at the LNA output. In order not to reject the desired signal as well, a notch filter in the feed-forward path is needed to distinguish the signal from the blocker. The notch filter should be centered at the desired RF bandwidth, rejecting the wanted signal, but must be sharp enough to pass the blocker, But feedforward techniques limited to narrow band design and are used for attenuating close-in interferers at RF is described [12]- [30]

#### 2.3.1.2 Feedback Interference Cancellation

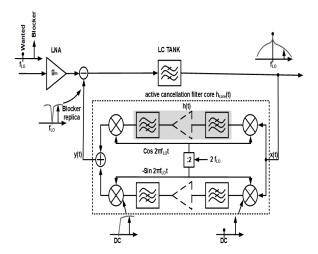

In this technique RF bandpass filtering using feedback interference cancellation are made. The concept of active feedback interference cancellation is shown in Fig. 2.10 [31]. The incoming wanted and blocker signal are amplified by an LNA with LC tank load. The output signal

Figure 2.9: Feedforward linearization technique

is fed into the active cancellation filter core and downconverted to baseband by the receiver local oscillator signal. In order to boost the open loop gain, baseband amplifiers might be necessary. The wanted signal is eliminated by highpass filtering, a blocker replica is upconverted to RF and subsequently subtracted from the incoming blocker signal at the output of the LNA transconductor stage thus resulting in a partial cancellation of the blocker signal. In that sense, the interference cancellation loop acts as a control loop which suppresses the blocker by the open loop gain.

Figure 2.10: Block diagram of feedback cancellation mechanism.

Similar to feedforward, feedback techniques also has some constraint, note that the mixers act as up and downconverters simultaneously in this technique. Thus, the downconversion mixer

does not only generate a baseband component but also an RF signal at twice the LO frequency. All issues are discussed in detail [31]. Thus, it is difficult to design if IF bandwidth is more.

Our aim to design a receiver having bandwidth (0.3G-3G) for radar and satellite application, which covers L band, S band. Due to many application like aircraft radar, TV broadcasting, mobile and cell phones, Wi-Fi, bluetooth, Taxi wireless, wireless LAN, cordless phone. ameteur wireless, private wireless, microwave, satellite communication etc it (multiband receiver) demands strong out of band blocker rejection technique. Our aim to reject out-band interferer signals at the input stage in such a way that there will not be much extra increase in power consumption and no effect on noise figure and other parameters. For these kind of wide band receiver a simplest multipath (auxiliary) receiver approach has proposed for multiband design. In main path receiver, a high gain differential LNA with bandwidth enhanced noise figure minimization technique and a passive mixer with linearity improved integrated baseband filter are proposed, and verified in CMOS process. For out of band sensing a auxiliary receiver (subthreshold) receiver is designed and verified in CMOS process. Specification of receiver for radar and military application is given in Table 2.2.

| Standard | frequency bands        | Gain (dB) | NF (dB) | IIP3 (dBm) |

|----------|------------------------|-----------|---------|------------|

| L1       | $1575.42 \mathrm{MHz}$ | 51dB      | 3       | -5         |

| L2       | $1227.6 \mathrm{MHz}$  | 53dB      | 4       | -9         |

| L3       | 1176.45 MHz            | 55 dB     | 3       | -10        |

| S        | 2750MHz                | 27        | 3.88    | -15        |

| S        | 27750MHz               | 27.29     | 4.07    | -12        |

| S        | 2800MHz                | 26.49     | 4.31    | -11        |

| S        | $2825 \mathrm{MHz}$    | 26.35     | 4.37    | -16        |

| S        | $2850 \mathrm{MHz}$    | 25.71     | 4.56    | -13        |

| GSM      | 0.8-1.9GHz             | 30        | max 9dB | -16        |

| 3GPP-LTE | 0.8 - 2.6 GHz          | 30        | 3dB     | -6         |

| WiMAX    | 2.4 - 3.5 GHz          | 30        | 3.5     | -11        |

| DVB-H    | 0.47-1.7GHz            | 30        | 3       | -8         |

| WLAN     | 2.4-5GHz               | 30        | 5       | -8         |

Table 2.2: Receiver specification for radar and satellite Application

## 2.4 Proposed Design Concern on Wireless Receiver Approach

#### 2.4.1 Identified Blockers and Strength

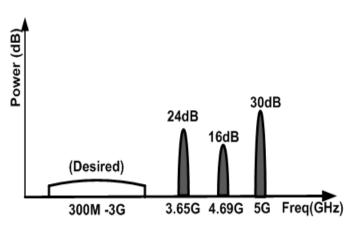

Indentified interfenence in between frequency range 2-5GHz, is Wi-Fi. There are basically five frequency bands used for Wi-Fi technology, 2.4GHz, 3.65GHz, 4.9GHz, 5GHz, 5.9GHz. So 3 - 5 GHz ultra wide band identified interference are 3.65GHz, 4.9GHz and 5GHz shown in Fig. 2.11. Most wireless products use the following Wi-Fi spectrums: 802.11a, 802.11b, 802.11g, 802.11n, 802.11ac.

Figure 2.11: Identified out of band blocker

#### 2.4.2 Proposed Design Approach

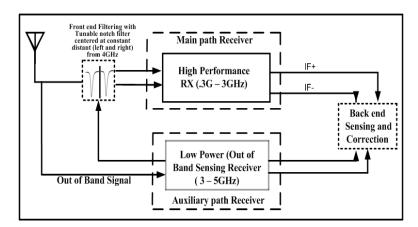

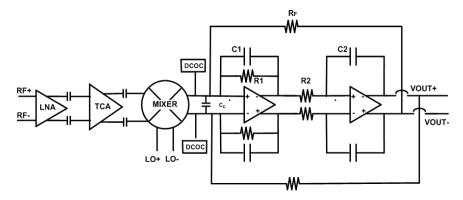

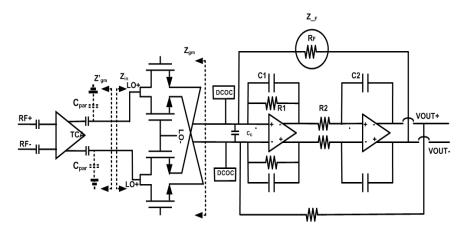

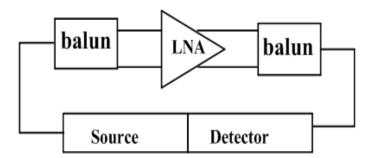

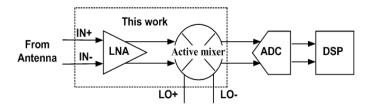

High Performance receiver (0.3G-3G) with subthreshold out of band sensing Receiver shown in Fig. 2.12. Subthreshold receiver is designed in such a way that it doesn't consume much power, senses out of band signal (3-5) GHZ and tuned the notch filters accordingly to reject out of band blocker at input. Two tunable notch filter centered at 4GHz is used and can be tuned from 3-4GHz or 4-5GHz constant distance (left and right from 4GHz).

An architecture of proposed approach for interference cancellation in receivers is shown in Fig. 2.12. The receiver consists of two paths. The front-end high performance receiver having

Figure 2.12: High Performance CMOS Wide-Band RF Front-End With Subthrehold Out of Band Sensing

differential LNA and down-conversion mixers form the main path is assumed to employ direct down-conversion. An auxiliary path receiver includes subthreshold LNA down-conversion mixers connected to the input of the main path which senses the out of band interferences and tune the notch filters located at fixed frequency 4GHz and tunes left and right from 4GHz according to the available RF band. The RF power incident on the antenna is assumed to consist of a desired signal and interferers. In the auxiliary path, the receiver will tune the notch filter for out of band frequency (3GHz - 5GHz) so that main receiver doesn't get saturate with interferers. If any out of band frequency interferer is present auxiliary path receiver with tune the notch filter to reject or attenuate the interferer. Tunable notch filters are used to attenuate interferers. If any blocker left, is down-converted to baseband with a local oscillator frequency (LO) are corrected by using back end correction. Back end sensing and correction can be done by using digital cancellation mechanism as used in [12].

#### 2.5 Summary

This chapter has explored the fundamentals of RF receivers and its key performance parameters in brief. A review of effect of blocker and transmitter leakage on receiver has been presented. Various blocker rejection techniques has been studied. Among different techniques, Mutiband with each path saw in not good approach, as it makes receiver narrow band. Further feedward

and feedback techniques came into picture but these techniques are either for RF close-in band interferences or very complicated to design. Among this these techniques are for narrow band design. After looking all techniques multipath receiver seems to be a good one, so for radar and satellite application, a low noise wideband receiver with subthreshold out of band sensing solution has approached.

### Chapter 3

# High Performance Low Noise Main Path Receiver

#### 3.1 Introduction

In a receiver, the low-noise amplifier (LNA) serves as the first amplification block along the receiving path. As it is one of the most critical building blocks of the receiver, since its performance greatly affects both the sensitivity and selectivity of the system. In this chapter, we will analyze the basic properties of a CMOS LNA. Starting with a discussion of receiver specification in section 3.2. Finally, will present a review of input matching and noise cancellation techniques of low-noise amplifier topologies, followed by analyses of input matching, noise, gain, bandwidth, implementation and measurement result.

In the next section, we will discuss the architecture of the demodulator, The mixer is one the most important nonlinear blocks in all wireless receivers. The primary function of a mixer is to perform frequency translation of the signal between the carrier frequency and baseband. The mixer's performance strongly affects the overall performance of the receiver, and it is a major nonlinear component in the receiver front-end. Finally we will discuss the architecture of the demodulator, followed by the circuit details of the various blocks, then implementation, measurement results of complete receiver and conclusions.

A review of performance of recently reported low noise wide band receiver is listed in Table 3.1. For wideband operation choice of LNA and mixer topologies plays very important role. Various paper of LNA and mixer paper has been reviewed and listed in below sections. Low noise composite transistor pair LNA is better topology for desired bandwidth (WB) and further inductive degeneration is used for bandwidth extension. Similarly for down conversion mixer, passive mixer is the best one for low noise, power and direct conversion. In below sections, wideband input matching and noise cancellation topologies of LNA and downconversion mixer operation are discussed in detail.

NF  $\overline{IIP_3}$  $\overline{P}_{DC}$  $\overline{\mathrm{VDD}}$ Tech. Area Freq.  $A_v$ Ref.  $S_{11}$ (GHz) (dB) (dB) (dBm) (Volts) (mW)  $(um^2)$ (nm) 13 0.3 - 2.958 <-10 1.9 - 2.1+121.3 49.4-99.8 40 1100\*1100 2000\*2000 32 0.05 - 2.480 <-10 5.5 27 1.2/2.560 65  $\overline{2.5}$  $3.5 \ 7$  $\overline{29}$ 0.4 - 436 <-15 38.4-55.2 65 1500\*1000  $\overline{[33]}$ 0.6 - 342 - 28-14 1.2 <-8 3 30 130

Table 3.1: Review of recent wideband receiver

#### 3.2 Wide Band Receiver Design Specification

#### 3.2.1 Sensitivity

Sensitivity of receiver is normally taken as the minimum input signal  $(S_{min})$  required to produce a specified output signal having a specified signal-to-noise (S/N) ratio and is defined as the minimum signal-to-noise ratio times the mean noise power given by (3.1). Sensitivity is expressed in terms of dBm (decibels relative to one milliwatt) power level along with reference impedance (usually  $50\Omega$ ) at the matched input condition.

$$S_{min}(dBm) = -174 + 10 * Log_{10}(BW) + NF_{rx} + SNR_{min}$$

(3.1)

where BW is signal bandwidth,  $NF_{rx}$  is total receiver noise figure, and  $SNR_{min}$  is minimum required signal-to-noise ratio. If  $T_0 = 290K$ .

#### 3.2.2 Noise Figure

Sensitivity and system noise figure are two closely related parameters for a wireless receiver. Noise Figure (NF) is the parameter which impacts the achievable sensitivity of a receiver. The relation between sensitivity and noise figure is given in (3.1). Noise factor F is defined as the ratio of input signal-to-noise  $SNR_{IN}$  to output signal-to-noise  $SNR_{OUT}$ . Noise figure NF is actually the noise factor in dB, i.e.

$$NF = 10 * \log(F) = 10 * SNR_{IN}/SNR_{OUT}$$

$$(3.2)$$

#### 3.2.3 Selectivity

Selectivity is the maximum signal level that a receiver can demodulate, and decode the information without an error in the presence of much stronger interferers (in-band/out-of-band). Selectivity of any receiver depends on filter sharpness of both RF band select filter and IF channel select filter, the dynamic range and circuit non-linearity.

#### 3.2.4 Linearity

In practical scenario no system is purely linear. which always distorts the output signal when the input signal level is above some threshold value. The inherent non-linear transfer characteristics of active devices (like BJT, MOS) impose this threshold. A practical non-linear system may be represented as

$$y_t = a_0 + a_1 * x_t + a_2 * x_t^2 + a_3 * x_t^3 + \dots$$

(3.3)

However, we are interested in achieving a linear system by making all coefficients other than first order gain  $(a_1)$  zero. Effects of non-linearity are specified by various parameters such as Harmonic Distortion (HD), gain compression (1-dB compression point), cross-modulation and intermodulation distortion  $(IIP_2, IIP_3)$ .

#### 3.3 Receiver Front-End Architecture

In order to achieve the highest level of simplicity, we have chosen a direct-conversion architecture for the front-end. Fig. 3.1 shows the block diagram of the circuit; the key building blocks include a low-noise amplifier, a demodulator, and a 2nd-order low-pass filter. The detailed design considerations for these blocks will be discussed in later sections.

Figure 3.1: Front end Block Diagram

#### 3.3.1 Target Specification

Targeted Specification for full system shown in Table 3.2.

Table 3.2: Full system specification of main path receiver

| Parameters      | Full System      |

|-----------------|------------------|

| Conversion Gain | > 30             |

| Bandwidth       | 0.3G - 3G        |

| IF frequency    | $5~\mathrm{MHz}$ |

| S11(dB)         | < -10            |

| NF(dB)          | <3               |

| CP1dB(dBm)      | > -29            |

| IIP3            | > -10            |

| Parameters      | LNA       | Mixer     |

|-----------------|-----------|-----------|

| Conversion Gain | > 15      | > 15      |

| Bandwidth       | 0.3G - 3G | 0.3G - 3G |

| IF frequency    | -         | 5MHz      |

| S11(dB)         | < -10     | -         |

| NF(dB)          | <2        | <2        |

| CP1dB(dBm)      | > -5      | > -10     |

| IIP3            | > 0       | > -5      |

#### 3.4 Circuit Implementations

#### 3.4.1 Wide Band Low Noise Amplifier (LNA)

In this section we will discuss detailed implementations of the front-end, covering all the major building blocks. The overall gain, noise figure and linearity requirement of a receiver front-end are partitioned and appropriate values of the same are assigned to individual sub-blocks such as LNA, mixer etc. Hence, framing specifications for LNA is completely dependent on receiver specifications and the successive sub-blocks in the receiver. Hence, a review of recently reported state of the art wide-band LNAs is done and the same is listed in Table 3.3.

Table 3.3: Review of recent wideband LNA

| Ref.      | Freq.<br>(GHz) | $A_v$ (dB) | $S_{11}$ | NF<br>(dB) | (dBm)       | VDD<br>(Volts) | $P_{DC}$ (mW) | Tech.<br>(nm) | Topology                                |

|-----------|----------------|------------|----------|------------|-------------|----------------|---------------|---------------|-----------------------------------------|

|           | 0.1 - 2        | 17.5       | <-10     | 2.9 - 3.5  | 10.6 - 14.3 | 2.2            | 21.34         | 180           | Complementry NMOS PMOS pair             |

| [34]JSSC  |                |            |          |            |             |                |               |               |                                         |

| 2017      |                |            |          |            |             |                |               |               |                                         |

| [35]      | 0.2 - 3.8      | 11.2       | <-10     | 2.55-2.85  | -2.7        | 1.2            | 1.9           | 65            | dual capacitive cross-coupling          |

| TCASII    |                |            |          |            |             |                |               |               |                                         |

| 2007      |                |            |          |            |             |                |               |               |                                         |

| 200.      | 0.05 - 0.860   | 15         | <-15     | 2.5        | 8.5         | 1.8            | 7.2           | 180           | NMOS load and an extra signal feed      |

| [36]ASSCC |                |            |          |            |             |                |               |               | -forward and noise-canceling path       |

| 2007      |                |            |          |            |             |                |               |               |                                         |

|           | 0.1 - 2.3      | 21         | <-8      | 1.7 (dSB)  | -1.5        | 1.8            | 18            | 90            | Composite NMOS/PMOS pair                |

| [37]JSSC  |                |            |          | , ,        |             |                |               |               | , -                                     |

| 2011      |                |            |          |            |             |                |               |               |                                         |

|           | 0.7 - 2.7      | 17.3       | <-8      | 2 (dSB)    | 5           | 1.8            | 17.1          | 180           | Common gate LNA with noise cancellation |

| [38]MTT-  |                |            |          | ļ , , , ,  |             |                |               |               | _                                       |

| S 2011    |                |            |          |            |             |                |               |               |                                         |

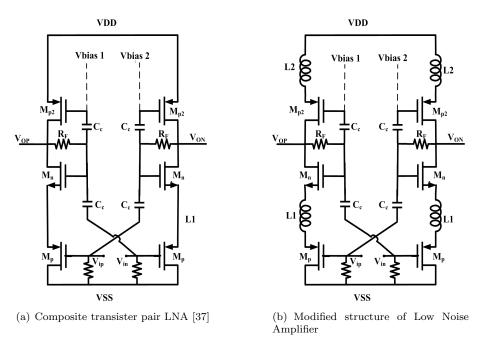

The main issue concerning the broadband amplifier topologies is their inferior noise performance and wide band input matching for radio applications. A noise cancellation technique usually applied to a shunt-shunt feedback amplifier [39] to reduce the amplifier thermal noise figure below 3 dB, while maintaining broadband impedance matching from 2 to thousands of MHz and voltage gain of 20 dB. Further CG-CS noise canceling LNA came in picture. It cancels noise by introducing two stage. Various topology of LNA has been listed in Table 3.3. So composite transistor pair is better choice for wide band with low noise. This chapter will take on this task and analyze the noise cancellation with composite NMOS/PMOS cross coupled transistor pair in detail.

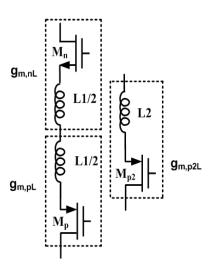

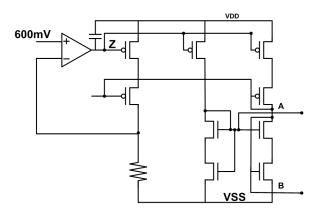

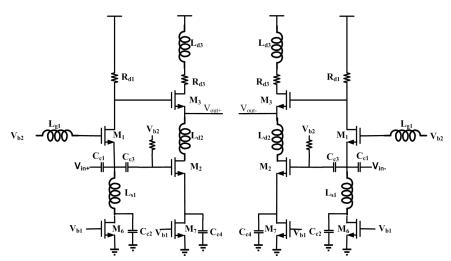

#### 3.4.1.1 Composite Transistor Pair Bandwidth Enhanced Low noise amplifier (LNA)

Fig. 3.2(b) shows the modified proposed structure of LNA. The LNA core utilize the composite NMOS/PMOS transistor pair configuration. In this configuration, LNA incorporates a composite NMOS/PMOS cross-coupled transistor pair [37] techniques to increase the amplification while partially cancelling the noise generated by the input transistors. Proposed LNA gain bandwidth and input matching is enhanced in the form of inductive degenerative composite NMOS/PMOS cross coupled transistor pair, noise figure is improved by using low threshold voltage MOS (LVT CMOS). A source follower buffer is added for output matching and measurement purposes.

Figure 3.2: Proposed struture of LNA

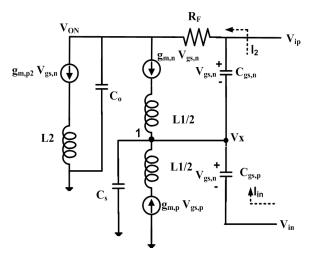

**3.4.1.1.1 Input Matching Analysis** The input impedance  $Z_{in,x}$  of Fig. 3.2(b) is derived using the half circuit small signal model. Small signal model of the proposed LNA is given by Fig. 3.3(a). By applying KCL in node 1

$$I_{in} = (V_{ip} - V_X)/(sC_{(gs,n)}) + V_X/sC_s - g_{(m,pL)}V_{(gs,p)} - g_{(m,nL)}V_{(gs,n)}$$

(3.4)

- (a) Equivalent half circuit small signal model to find the input impedance of proposed Low Noise Amplifier

- (b) Inductive degeneration of NMOS and PMOS

Figure 3.3: Equivalent small signal model of LNA

$$I_{in} = (V_{ip} - V_X)/(sC_{(gs,n)}) + V_X/sC_s - g_{(m,pL)}(V_{in} - V_X) - g_{(m,nL)}(V_X - V_{ip})$$

(3.5)

$$I_2 = (V_{ON} - V_{ip})/R_F = g_{(m,nL)}V_{(gs,n)} = (V_X - V_{ip})/(sC_{(gs,n)})$$

(3.6)

$$V_x = V_{in} - I_{in} s C_{(gs,P)} (3.7)$$

$$\frac{V_{in}}{I_{in}} = Z_{in} = \frac{1}{\frac{1+A_v}{R_F||1/sC_{gd,n}} + \frac{s(C_{gs,p} + C_{gs,n})(2g_{m,nL} + sC_s)}{g_{m,nL} + gm,pL + sC_s}}$$